Z77A-G41 specifications

The MSI Z77A-G41 motherboard is a feature-rich solution designed for users looking to build a powerful yet budget-friendly system. Built on the Intel Z77 chipset, the Z77A-G41 supports Intel's 3rd generation Core processors, offering significant performance enhancements and features for gamers, content creators, and everyday users alike.One of the standout features of the Z77A-G41 is its support for dual-channel DDR3 memory. This motherboard can accommodate up to 16GB of RAM across its four DIMM slots, supporting frequencies ranging from 1066MHz up to 3000MHz (OC). This allows for robust multitasking capabilities and improved system responsiveness, making it an excellent choice for memory-intensive applications.

In terms of connectivity, the MSI Z77A-G41 provides ample options with its multiple USB ports, including USB 3.0 and USB 2.0 connectors. The inclusion of USB 3.0 allows for faster data transfers, essential for users who rely on external drives and peripherals. Additionally, the motherboard features SATA III ports, enabling high-speed data access for SSDs and HDDs.

The Z77A-G41 also incorporates MSI's Military Class III components, ensuring increased stability and durability. These components provide enhanced longevity and reliability, minimizing the chances of hardware failure, which is particularly important for users looking for a long-lasting build.

Gaming enthusiasts will appreciate the motherboard’s support for AMD CrossFire technology. This allows users to install multiple graphics cards for improved gaming performance and visual quality. Alongside, the motherboard integrates the latest audio technologies, providing a rich sound experience for gamers and multimedia consumers.

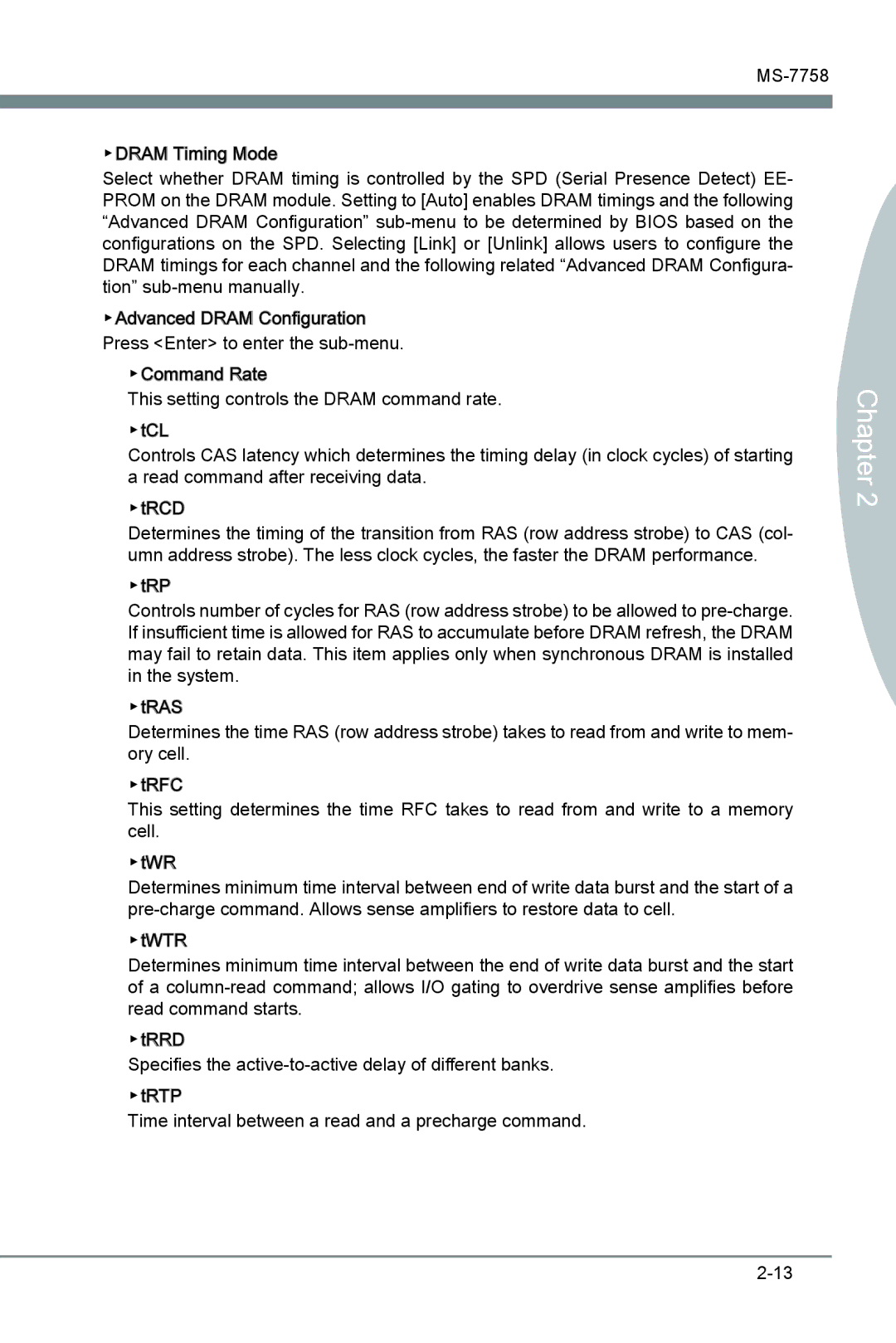

Another valuable feature is the Click BIOS 2, which offers a user-friendly interface for system configuration and overclocking. This intuitive BIOS interface grants users easy access to adjust settings and optimize performance with just a few clicks.

The MSI Z77A-G41 is a versatile and dependable motherboard suitable for a wide range of applications. With its robust design, excellent memory support, and advanced connectivity options, it provides an optimal foundation for both gaming rigs and general-purpose systems. Whether you’re looking to build a high-performance workstation or an affordable gaming setup, the Z77A-G41 stands out as an excellent choice, delivering reliable performance and an array of features that cater to different user needs.