Contents

DSCLP-200/300

Page

Serial Number

Declaration of Conformity

Table of Contents

General Information

Hardware Configuration

RS-422 or RS-485 Signal Line Termination

Signal Connections

Full-duplex/Half-duplex Operation

2 AUX0SEL1,0, AUX1SEL1,0 J12,11,19,18

1 CTS0SEL, CTS1SEL J10,17

RCLK0SEL, RCLK1SEL J13

RXEN0SEL, RXEN1SEL J16

Enable Scratchpad Register SPAD, J2

4 TGL0SEL1,0, TGL1SEL1,0 J15,14,22,21

Clock Rate and Optional Registers

Enable scratchpad registers

Force High-Speed Uart Clock X2 or X4, J4-J5

X4 mode

Hardware Installation

Jumper/connector locations

Address Map and Special Registers

Base Address and Interrupt Level IRQ

Enabling the Special Registers

Interrupt Status Register

Quatech Modem Control Register

Quatech Modem Control Register

Options Register

Enhanced Serial Adapter Identification

Clock Rate Multiplier

RR1 RR0

Windows Configurations

Windows Millennium

Windows

Windows

Windows Using the New Hardware Found Wizard

Viewing Resources with Device Manager

Page

Page

Page

OS/2

Other Operating Systems

Windows NT

DOS and other operating systems

QTPCI.EXE Basic Mode display

QTPCI.EXE Expert Mode display

External Connections

Jumper/Channel correspondence

RTS/CTS Handshake

Rclk

Xclk

AUXIN/AUXOUT Loopback

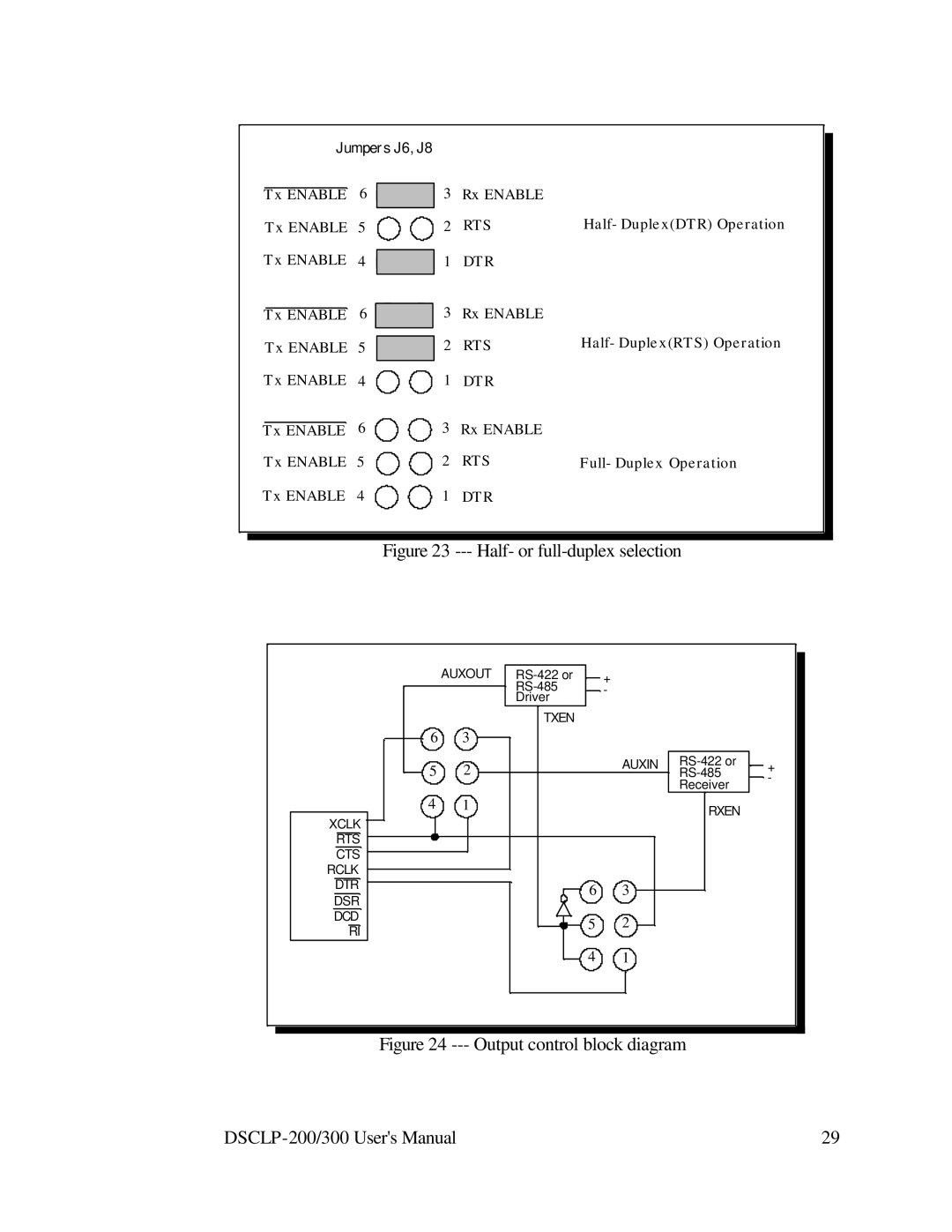

Half-Duplex/Full-Duplex Selection

Half- or full-duplex selection

Termination Resistors

RS-422/485 Line termination resistance values

DSCLP-200/300 connector definitions

RS-422/485 Peripheral Connection

PCI Resource Map

INTA#

Specifications

With 64-byte FIFOs optional

Troubleshooting

Computer will not boot up

DSCLP-200/300 Revision December