CDX-CA850/CA850X/CA860X

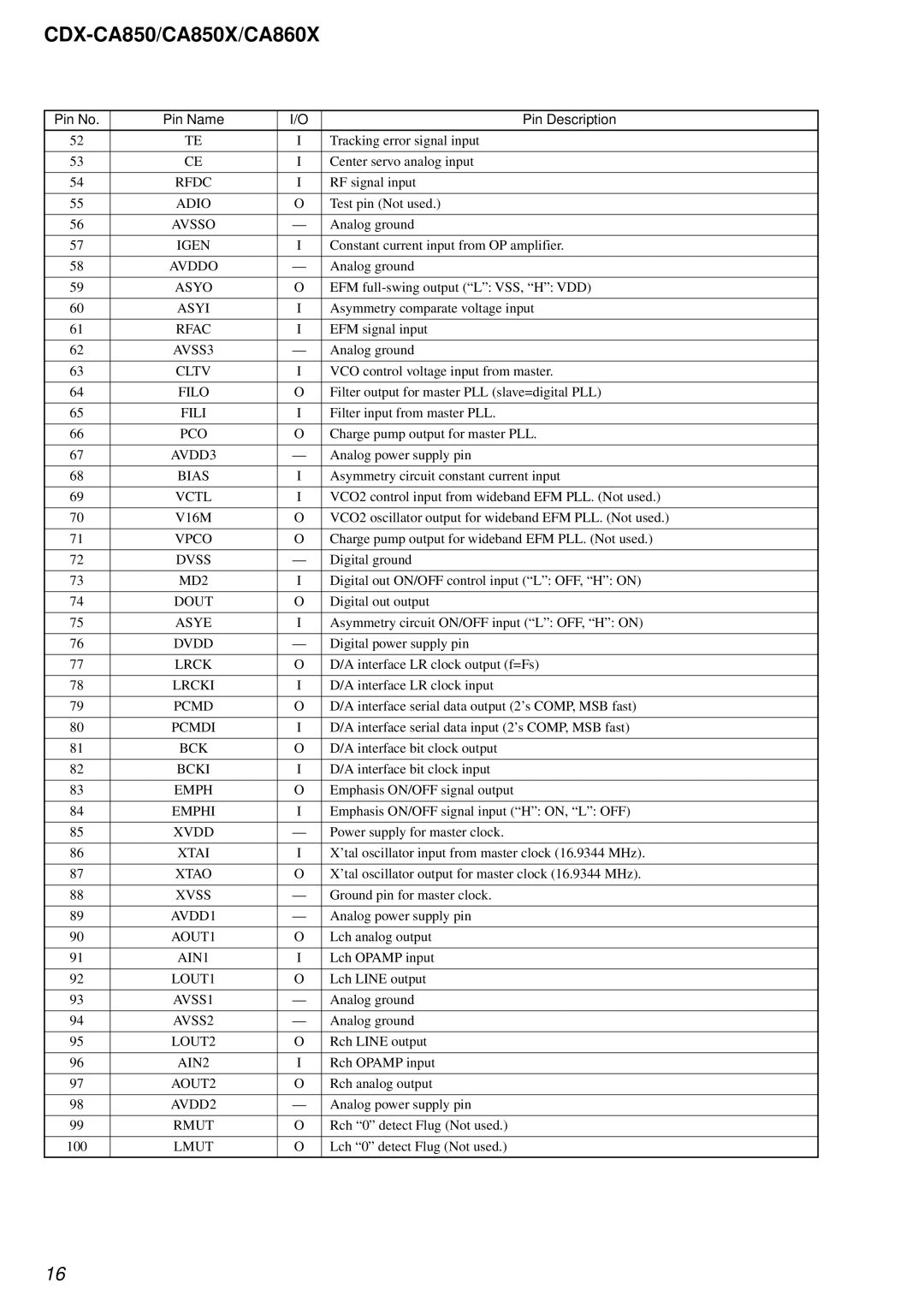

Pin No. | Pin Name | I/O | Pin Description |

|

|

|

|

52 | TE | I | Tracking error signal input |

|

|

|

|

53 | CE | I | Center servo analog input |

|

|

|

|

54 | RFDC | I | RF signal input |

|

|

|

|

55 | ADIO | O | Test pin (Not used.) |

|

|

|

|

56 | AVSSO | — | Analog ground |

|

|

|

|

57 | IGEN | I | Constant current input from OP amplifier. |

|

|

|

|

58 | AVDDO | — | Analog ground |

|

|

|

|

59 | ASYO | O | EFM |

|

|

|

|

60 | ASYI | I | Asymmetry comparate voltage input |

|

|

|

|

61 | RFAC | I | EFM signal input |

|

|

|

|

62 | AVSS3 | — | Analog ground |

|

|

|

|

63 | CLTV | I | VCO control voltage input from master. |

|

|

|

|

64 | FILO | O | Filter output for master PLL (slave=digital PLL) |

|

|

|

|

65 | FILI | I | Filter input from master PLL. |

|

|

|

|

66 | PCO | O | Charge pump output for master PLL. |

|

|

|

|

67 | AVDD3 | — | Analog power supply pin |

|

|

|

|

68 | BIAS | I | Asymmetry circuit constant current input |

|

|

|

|

69 | VCTL | I | VCO2 control input from wideband EFM PLL. (Not used.) |

|

|

|

|

70 | V16M | O | VCO2 oscillator output for wideband EFM PLL. (Not used.) |

|

|

|

|

71 | VPCO | O | Charge pump output for wideband EFM PLL. (Not used.) |

|

|

|

|

72 | DVSS | — | Digital ground |

|

|

|

|

73 | MD2 | I | Digital out ON/OFF control input (“L”: OFF, “H”: ON) |

|

|

|

|

74 | DOUT | O | Digital out output |

|

|

|

|

75 | ASYE | I | Asymmetry circuit ON/OFF input (“L”: OFF, “H”: ON) |

|

|

|

|

76 | DVDD | — | Digital power supply pin |

|

|

|

|

77 | LRCK | O | D/A interface LR clock output (f=Fs) |

|

|

|

|

78 | LRCKI | I | D/A interface LR clock input |

|

|

|

|

79 | PCMD | O | D/A interface serial data output (2’s COMP, MSB fast) |

|

|

|

|

80 | PCMDI | I | D/A interface serial data input (2’s COMP, MSB fast) |

|

|

|

|

81 | BCK | O | D/A interface bit clock output |

|

|

|

|

82 | BCKI | I | D/A interface bit clock input |

|

|

|

|

83 | EMPH | O | Emphasis ON/OFF signal output |

|

|

|

|

84 | EMPHI | I | Emphasis ON/OFF signal input (“H”: ON, “L”: OFF) |

|

|

|

|

85 | XVDD | — | Power supply for master clock. |

|

|

|

|

86 | XTAI | I | X’tal oscillator input from master clock (16.9344 MHz). |

|

|

|

|

87 | XTAO | O | X’tal oscillator output for master clock (16.9344 MHz). |

|

|

|

|

88 | XVSS | — | Ground pin for master clock. |

|

|

|

|

89 | AVDD1 | — | Analog power supply pin |

|

|

|

|

90 | AOUT1 | O | Lch analog output |

|

|

|

|

91 | AIN1 | I | Lch OPAMP input |

|

|

|

|

92 | LOUT1 | O | Lch LINE output |

|

|

|

|

93 | AVSS1 | — | Analog ground |

|

|

|

|

94 | AVSS2 | — | Analog ground |

|

|

|

|

95 | LOUT2 | O | Rch LINE output |

|

|

|

|

96 | AIN2 | I | Rch OPAMP input |

|

|

|

|

97 | AOUT2 | O | Rch analog output |

|

|

|

|

98 | AVDD2 | — | Analog power supply pin |

|

|

|

|

99 | RMUT | O | Rch “0” detect Flug (Not used.) |

|

|

|

|

100 | LMUT | O | Lch “0” detect Flug (Not used.) |

|

|

|

|

16