GTR64 | http://www.matrix.es/GTR64 |

Clock synchronization can be used as a handshaking mechanism, to enable receivers to cope with fast data transfers. On a byte level, a slave (host

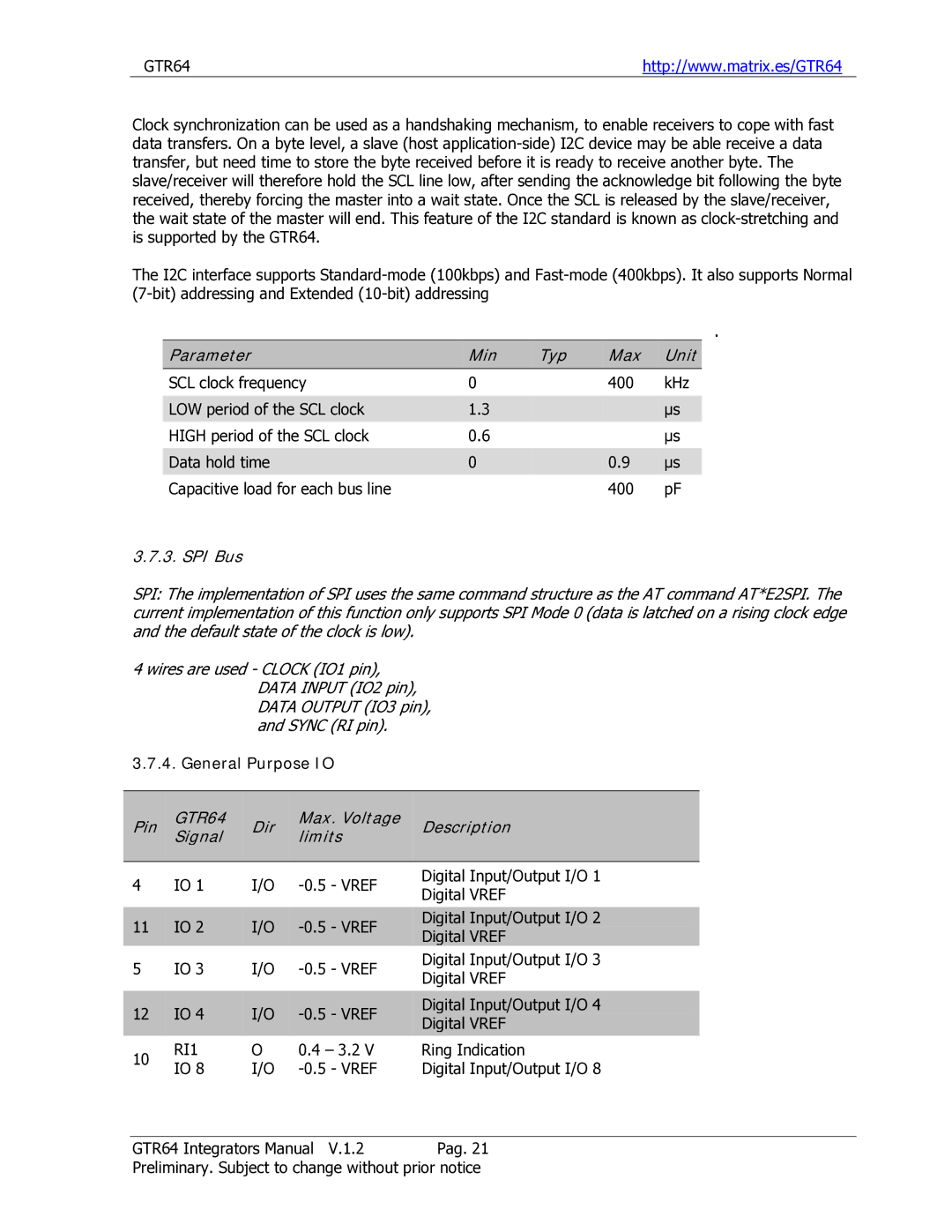

The I2C interface supports

.

Parameter | Min | Typ | Max | Unit |

SCL clock frequency | 0 |

| 400 | kHz |

|

|

|

|

|

LOW period of the SCL clock | 1.3 |

|

| μs |

HIGH period of the SCL clock | 0.6 |

|

| μs |

|

|

|

|

|

Data hold time | 0 |

| 0.9 | μs |

Capacitive load for each bus line |

|

| 400 | pF |

3.7.3. SPI Bus

SPI: The implementation of SPI uses the same command structure as the AT command AT*E2SPI. The current implementation of this function only supports SPI Mode 0 (data is latched on a rising clock edge and the default state of the clock is low).

4 wires are used - CLOCK (IO1 pin), DATA INPUT (IO2 pin), DATA OUTPUT (IO3 pin), and SYNC (RI pin).

3.7.4. General Purpose IO

| Pin |

| GTR64 |

| Dir |

| Max. Voltage |

| Description |

|

|

|

| Signal |

|

|

| limits |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 4 |

| IO 1 |

| I/O |

|

| Digital Input/Output I/O 1 |

| |

|

|

|

|

| Digital VREF |

| ||||

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

| 11 |

| IO 2 |

| I/O |

|

| Digital Input/Output I/O 2 |

| |

|

|

|

|

| Digital VREF |

| ||||

|

|

|

|

|

|

|

|

|

| |

| 5 |

| IO 3 |

| I/O |

|

| Digital Input/Output I/O 3 |

| |

|

|

|

|

| Digital VREF |

| ||||

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

| 12 |

| IO 4 |

| I/O |

|

| Digital Input/Output I/O 4 |

| |

|

|

|

|

| Digital VREF |

| ||||

|

|

|

|

|

|

|

|

|

| |

| 10 |

| RI1 |

| O |

| 0.4 – 3.2 V |

| Ring Indication |

|

|

| IO 8 |

| I/O |

|

| Digital Input/Output I/O 8 |

| ||

|

|

|

|

|

|

|

GTR64 Integrators Manual V.1.2 Pag. 21

Preliminary. Subject to change without prior notice