BIOS Setup Utility![]()

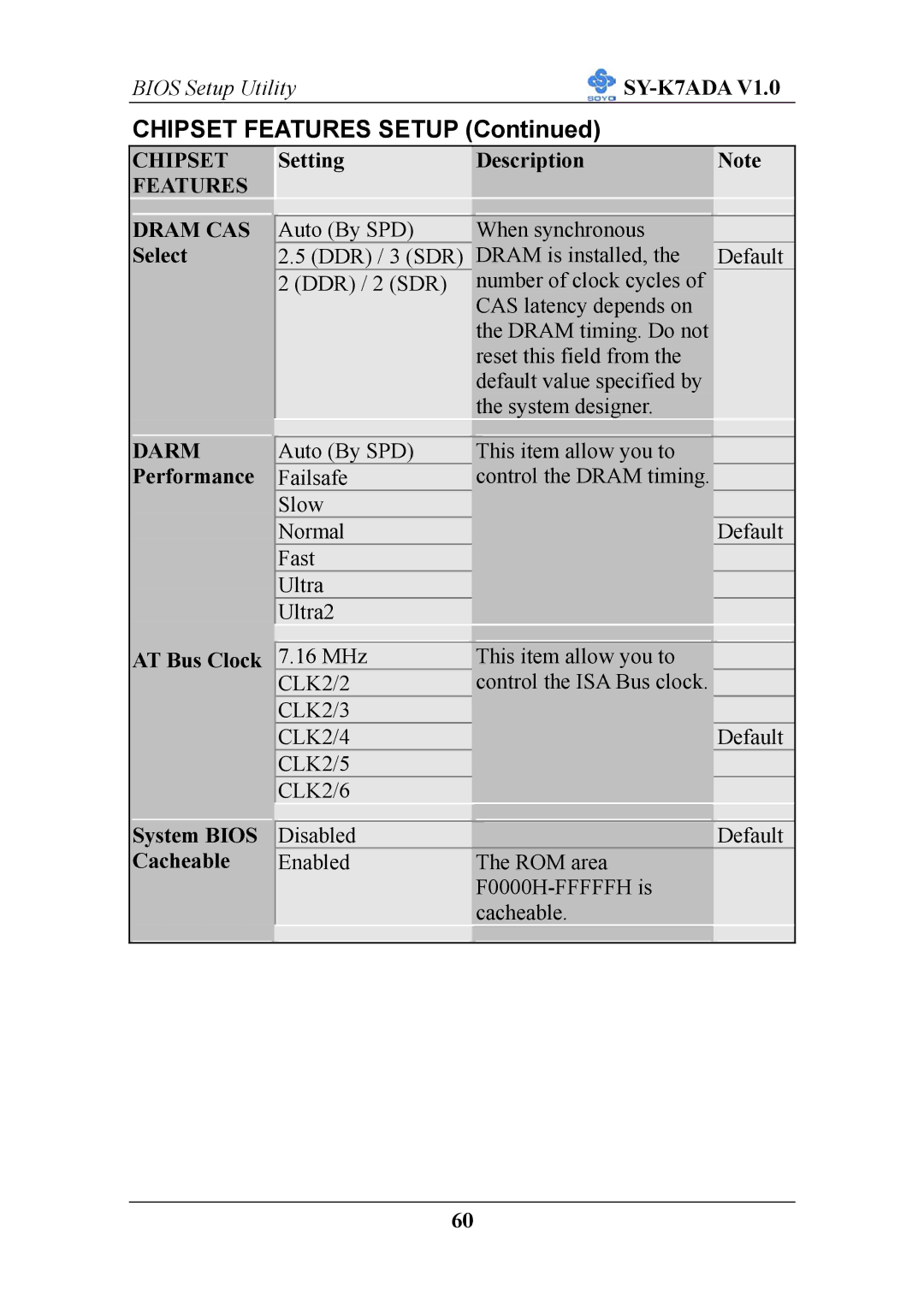

CHIPSET FEATURES SETUP (Continued)

| CHIPSET |

|

| Setting | Description | Note |

|

|

|

|

| ||||

| FEATURES |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DRAM CAS Select

Auto (By SPD)

2.5(DDR) / 3 (SDR) 2 (DDR) / 2 (SDR)

When synchronous ![]() DRAM is installed, the Default number of clock cycles of

DRAM is installed, the Default number of clock cycles of

CAS latency depends on the DRAM timing. Do not reset this field from the default value specified by the system designer.

DARM Performance

|

|

|

Auto (By SPD) | This item allow you to |

|

Failsafe | control the DRAM timing. |

|

Slow |

|

|

Normal |

| Default |

Fast |

|

|

Ultra |

|

|

Ultra2 |

|

|

|

|

|

AT Bus Clock

System BIOS Cacheable

7.16 MHz | This item allow you to |

|

CLK2/2 | control the ISA Bus clock. |

|

CLK2/3 |

|

|

CLK2/4 |

| Default |

CLK2/5 |

|

|

CLK2/6 |

|

|

|

|

|

Disabled |

| Default |

Enabled | The ROM area |

|

|

| |

| cacheable. |

|

|

|

|

60