www.ti.com | Registers |

3.2CMPTGT

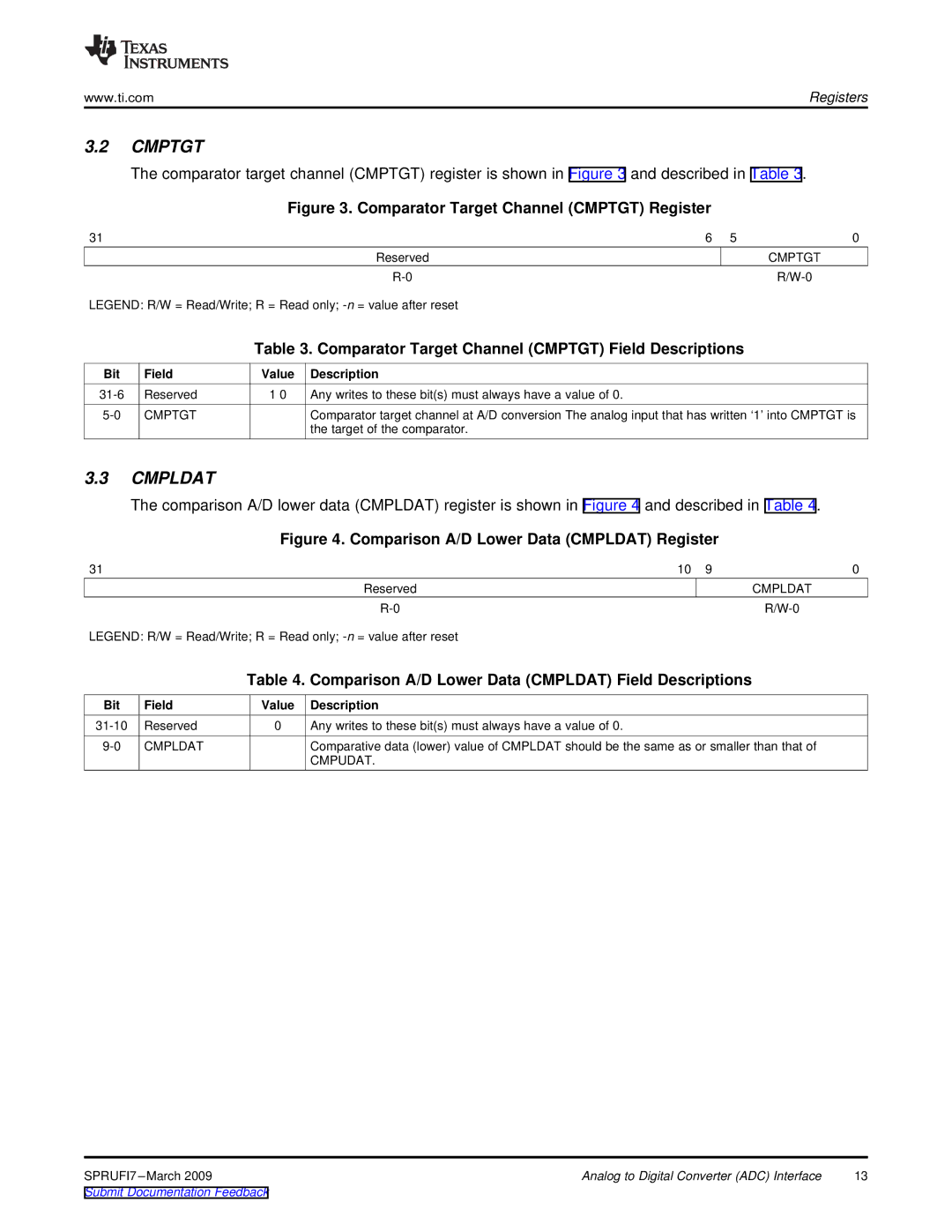

The comparator target channel (CMPTGT) register is shown in Figure 3 and described in Table 3.

Figure 3. Comparator Target Channel (CMPTGT) Register

31 | 6 | 5 | 0 |

Reserved |

|

| CMPTGT |

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 3. Comparator Target Channel (CMPTGT) Field Descriptions

Bit | Field | Value | Description |

Reserved | 1 0 | Any writes to these bit(s) must always have a value of 0. | |

CMPTGT |

| Comparator target channel at A/D conversion The analog input that has written ‘1’ into CMPTGT is | |

|

|

| the target of the comparator. |

3.3CMPLDAT

The comparison A/D lower data (CMPLDAT) register is shown in Figure 4 and described in Table 4.

Figure 4. Comparison A/D Lower Data (CMPLDAT) Register

31 | 10 | 9 | 0 |

Reserved |

|

| CMPLDAT |

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 4. Comparison A/D Lower Data (CMPLDAT) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Any writes to these bit(s) must always have a value of 0. | |

CMPLDAT |

| Comparative data (lower) value of CMPLDAT should be the same as or smaller than that of | |

|

|

| CMPUDAT. |

Analog to Digital Converter (ADC) Interface | 13 | |

Submit Documentation Feedback |

|

|