TPS54810

SLVS420B − MARCH 2002 − R EVISED FEBRUARY 2005

DETAILED DESCRIPTION |

| |||||||

Under Voltage Lock Out (UVLO) |

| VBIAS | pin. X7R | or X5R grade dielectrics are | ||||

| recommended because their values are more stable over | |||||||

The TPS54810 incorporates an under voltage lockout | temperature. The bypass capacitor should be placed close | |||||||

to the VBIAS pin and returned to AGND. |

| |||||||

circuit to keep the device disabled when the input voltage |

| |||||||

External loading on VBIAS is allowed, with the caution that | ||||||||

(VIN) is insufficient. During power up, internal circuits are | ||||||||

held inactive until VIN exceeds the nominal UVLO | internal circuits require a minimum VBIAS of 2.70 V, and | |||||||

threshold voltage of 3.80 V. Once the UVLO start threshold | external loads on VBIAS with ac or digital switching noise | |||||||

is reached, device | may degrade performance. The VBIAS pin may be useful | |||||||

until VIN falls below the nominal UVLO stop threshold of | as a reference voltage for external circuits. |

| ||||||

3.5 V. Hysteresis in the UVLO comparator, and a | Voltage Reference |

|

|

| ||||

rising and falling edge deglitch circuit reduce the likelihood |

|

|

| |||||

|

|

|

|

| ||||

of shutting the device down due to noise on VIN. |

| The voltage reference system produces a precise Vref | ||||||

|

| signal | by scaling the output of a | temperature stable | ||||

| bandgap circuit. During manufacture, the bandgap and | |||||||

|

|

| ||||||

The | scaling circuits are trimmed to produce 0.891 V at the | |||||||

pin acts as an enable (shutdown) control by keeping the | output of the error amplifier, with the amplifier connected | |||||||

device turned off until the voltage exceeds the start | as a voltage follower. The trim procedure adds to the high | |||||||

threshold voltage of approximately 1.2 V. When SS/ENA | precision regulation of the TPS54810, since it cancels | |||||||

exceeds the enable threshold, device start up begins. The | offset errors in the scale and error amplifier circuits. |

| ||||||

reference voltage fed to the error amplifier is | linearly | Oscillator and PWM Ramp |

|

| ||||

ramped up from 0 V to 0.891 V in 3.35 ms. Similarly, the |

|

| ||||||

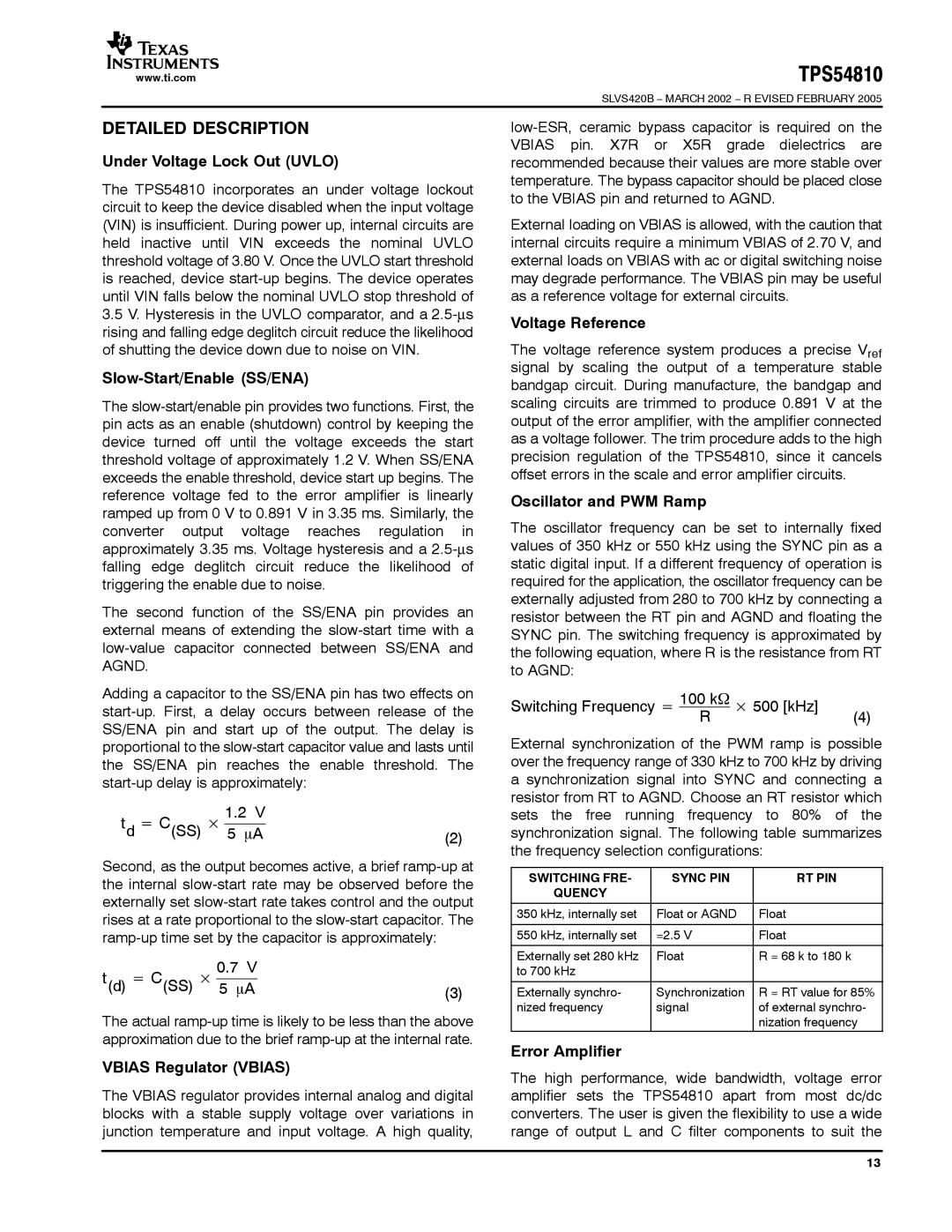

The oscillator frequency can be set to internally fixed | ||||||||

converter output voltage reaches regulation in | ||||||||

approximately 3.35 ms. Voltage hysteresis and a | values of 350 kHz or 550 kHz using the SYNC pin as a | |||||||

falling edge deglitch circuit reduce the likelihood of | static digital input. If a different frequency of operation is | |||||||

triggering the enable due to noise. |

| required for the application, the oscillator frequency can be | ||||||

The second function of the SS/ENA pin provides an | externally adjusted from 280 to 700 kHz by connecting a | |||||||

resistor between the RT pin and AGND and floating the | ||||||||

external means of extending the | ||||||||

SYNC pin. The switching frequency is approximated by | ||||||||

the following equation, where R is the resistance from RT | ||||||||

AGND. |

|

| ||||||

|

| to AGND: |

|

|

| |||

|

|

|

|

|

| |||

Adding a capacitor to the SS/ENA pin has two effects on | Switching Frequency + 100 kW | 500 [kHz] |

| |||||

delay occurs between release | of the |

| ||||||

|

| R |

| (4) | ||||

SS/ENA pin and start up of the output. The delay is |

|

|

| |||||

External synchronization of the PWM ramp is possible | ||||||||

proportional to the | ||||||||

the SS/ENA pin reaches the enable threshold. The | over the frequency range of 330 kHz to 700 kHz by driving | |||||||

| a synchronization signal into SYNC and connecting a | |||||||

| 1.2 V |

| resistor from RT to AGND. Choose an RT resistor which | |||||

td + C(SS) |

| sets the free running frequency to 80% of the | ||||||

5 mA | (2) | synchronization signal. The following table summarizes | ||||||

Second, as the output becomes active, a brief | the frequency selection configurations: |

| ||||||

|

|

|

|

| ||||

SWITCHING FRE- | SYNC PIN | RT PIN |

| |||||

the internal |

| |||||||

QUENCY |

|

|

| |||||

externally set |

|

|

| |||||

|

|

|

|

| ||||

350 kHz, internally set | Float or AGND | Float |

| |||||

rises at a rate proportional to the |

| |||||||

|

|

|

|

| ||||

550 kHz, internally set | =2.5 V | Float |

| |||||

| 0.7 V |

| Externally set 280 kHz | Float | R = 68 k to 180 k |

| ||

t(d) + C(SS) |

| to 700 kHz |

|

|

| |||

5 mA | (3) |

|

|

| ||||

Externally synchro- | Synchronization | R = RT value for 85% | ||||||

The actual | nized frequency | signal | of external synchro- | |||||

|

|

| nization frequency | |||||

approximation due to the brief | Error Amplifier |

|

|

| ||||

VBIAS Regulator (VBIAS) |

|

|

|

| ||||

| The high performance, wide bandwidth, voltage error | |||||||

The VBIAS regulator provides internal analog and digital | ||||||||

amplifier sets the TPS54810 apart from most dc/dc | ||||||||

blocks with a stable supply voltage over variations in | converters. The user is given the flexibility to use a wide | |||||||

junction temperature and input voltage. A high quality, | range of output L and C filter components to suit the | |||||||

13