|

|

| ||

|

| |||

|

| |||

2.5” Solid State Disk | ||||

| ||||

|

|

|

|

|

|

|

|

|

|

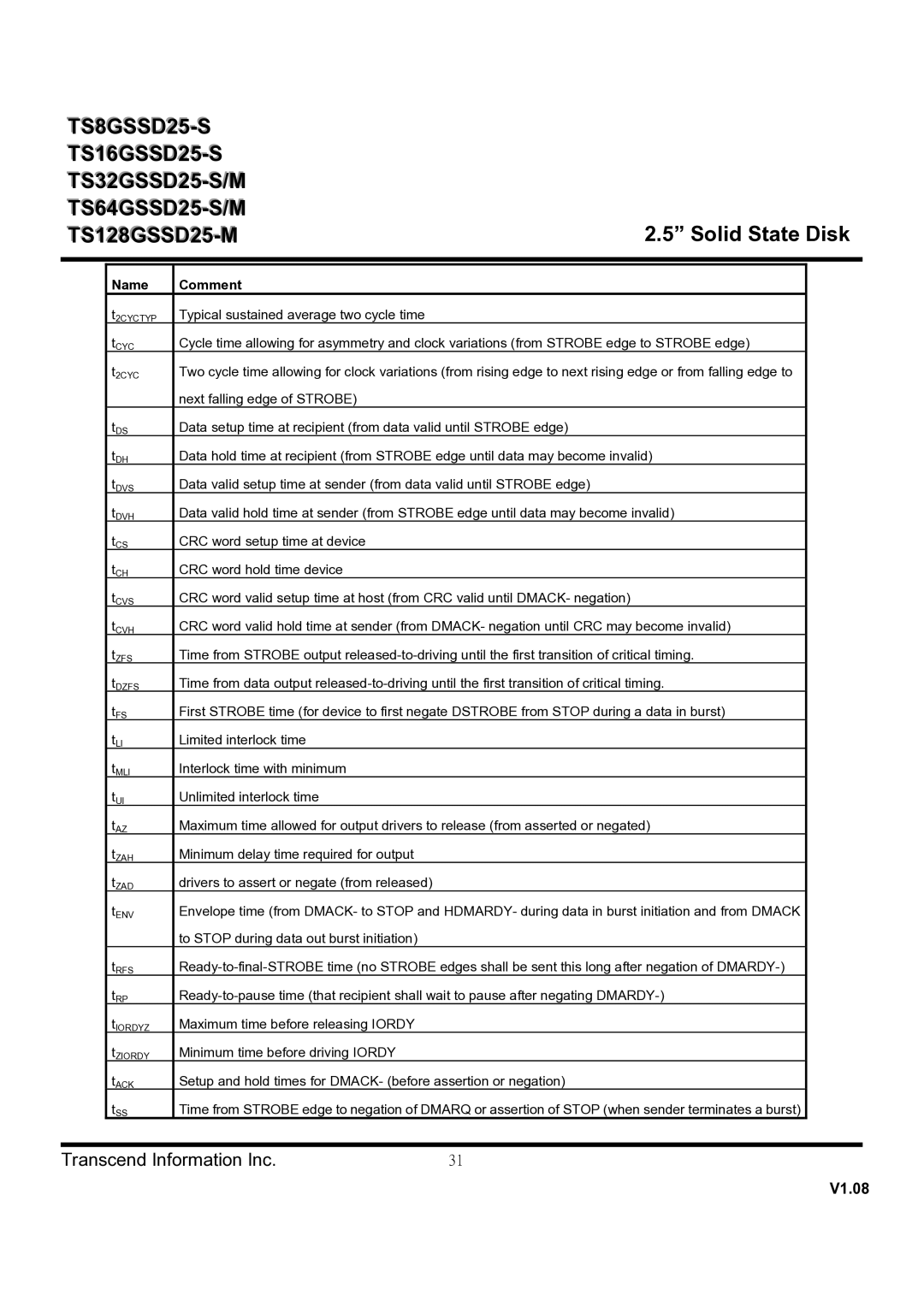

| Name | Comment |

|

|

| t2CYCTYP | Typical sustained average two cycle time |

|

|

| tCYC | Cycle time allowing for asymmetry and clock variations (from STROBE edge to STROBE edge) |

| |

| t2CYC | Two cycle time allowing for clock variations (from rising edge to next rising edge or from falling edge to |

| |

|

| next falling edge of STROBE) |

|

|

| tDS | Data setup time at recipient (from data valid until STROBE edge) |

| |

| tDH | Data hold time at recipient (from STROBE edge until data may become invalid) |

| |

| tDVS | Data valid setup time at sender (from data valid until STROBE edge) |

| |

| tDVH | Data valid hold time at sender (from STROBE edge until data may become invalid) |

| |

| tCS | CRC word setup time at device |

|

|

| tCH | CRC word hold time device |

|

|

| tCVS | CRC word valid setup time at host (from CRC valid until DMACK- negation) |

| |

| tCVH | CRC word valid hold time at sender (from DMACK- negation until CRC may become invalid) |

| |

| tZFS | Time from STROBE output |

| |

| tDZFS | Time from data output |

| |

| tFS | First STROBE time (for device to first negate DSTROBE from STOP during a data in burst) |

| |

| tLI | Limited interlock time |

|

|

| tMLI | Interlock time with minimum |

|

|

| tUI | Unlimited interlock time |

|

|

| tAZ | Maximum time allowed for output drivers to release (from asserted or negated) |

| |

| tZAH | Minimum delay time required for output |

|

|

| tZAD | drivers to assert or negate (from released) |

|

|

| tENV | Envelope time (from DMACK- to STOP and HDMARDY- during data in burst initiation and from DMACK |

| |

|

| to STOP during data out burst initiation) |

|

|

| tRFS |

| ||

| tRP |

| ||

| tIORDYZ | Maximum time before releasing IORDY |

|

|

| tZIORDY | Minimum time before driving IORDY |

|

|

| tACK | Setup and hold times for DMACK- (before assertion or negation) |

| |

| tSS | Time from STROBE edge to negation of DMARQ or assertion of STOP (when sender terminates a burst) |

| |

|

|

|

|

|

Transcend Information Inc. | 31 |

| ||

Page 31

Image 31