PCI32 Interface v3.0

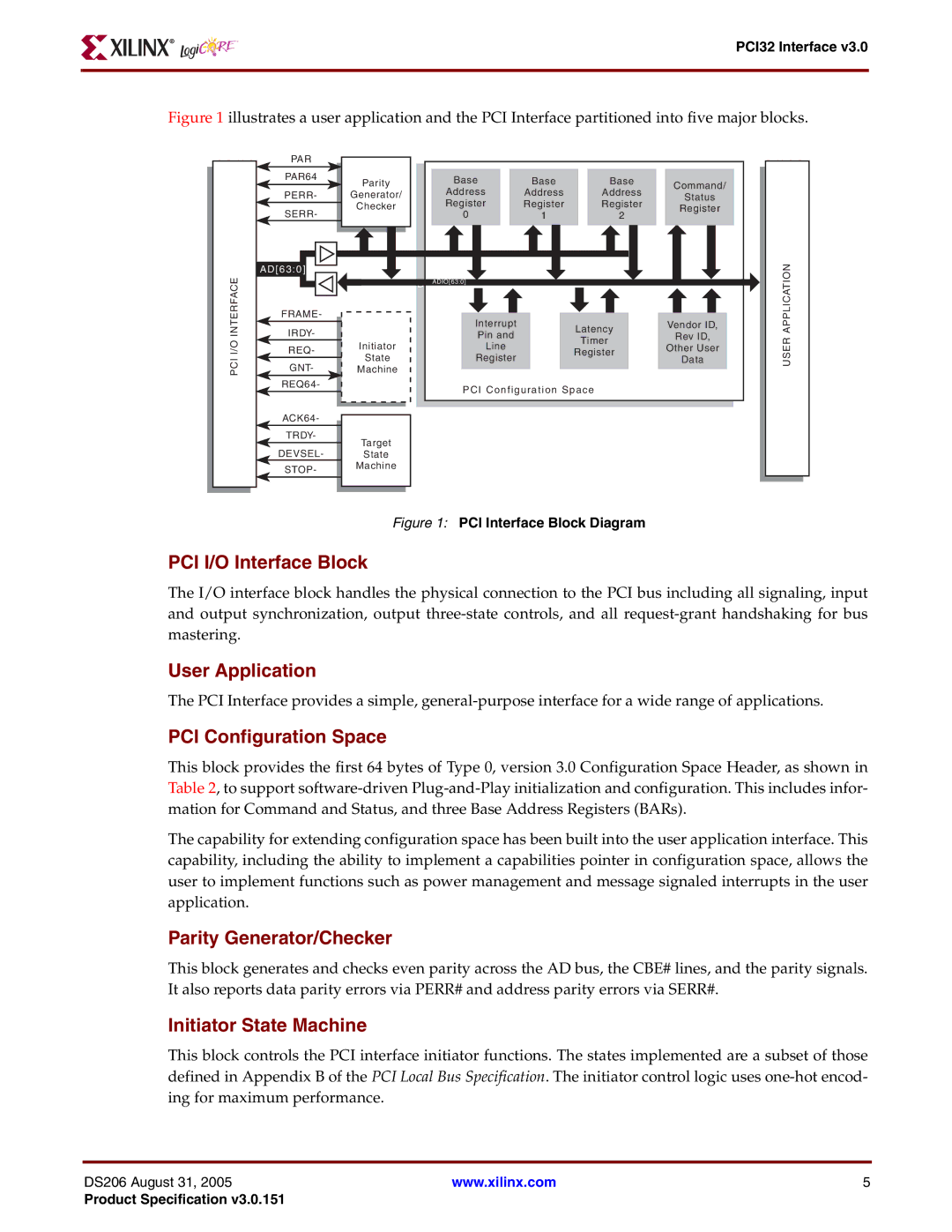

Figure 1 illustrates a user application and the PCI Interface partitioned into five major blocks.

PCI I/O INTERFACE

PAR

PAR64

PERR-

SERR-

AD[63:0] |

FRAME-

IRDY-

REQ-

GNT-

REQ64-

ACK64-

TRDY-

DEVSEL-

STOP-

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Parity |

|

|

|

| Base |

|

| Base |

|

| Base |

|

| Command/ |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

| Address |

| Address |

|

| Address |

|

|

| |||||||

|

| Generator/ |

|

|

|

|

|

|

|

|

| Status |

| ||||||||

|

|

|

|

|

| Register |

| Register |

|

| Register |

|

|

| |||||||

|

| Checker |

|

|

|

|

|

|

|

|

| Register |

| ||||||||

|

|

|

|

|

| 0 |

| 1 |

|

|

| 2 |

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

| ADIO[63:0] |

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

| Interrupt |

|

|

| Latency |

|

|

| Vendor ID, |

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

| Pin and |

|

|

|

|

|

| Rev ID, |

|

| ||||

|

| Initiator |

|

|

|

|

|

|

|

|

| Timer |

|

|

|

|

| ||||

|

|

|

|

|

|

| Line |

|

|

|

|

|

|

| Other User |

|

| ||||

|

|

|

|

|

|

|

|

|

| Register |

|

|

|

|

| ||||||

|

| State |

|

|

|

|

| Register |

|

|

|

|

|

| Data |

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

| Machine |

|

|

|

|

| PCI Configuration Space |

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Target |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

| State |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Machine |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

USER APPLICATION

Figure 1: PCI Interface Block Diagram

PCI I/O Interface Block

The I/O interface block handles the physical connection to the PCI bus including all signaling, input and output synchronization, output

User Application

The PCI Interface provides a simple,

PCI Configuration Space

This block provides the first 64 bytes of Type 0, version 3.0 Configuration Space Header, as shown in Table 2, to support

The capability for extending configuration space has been built into the user application interface. This capability, including the ability to implement a capabilities pointer in configuration space, allows the user to implement functions such as power management and message signaled interrupts in the user application.

Parity Generator/Checker

This block generates and checks even parity across the AD bus, the CBE# lines, and the parity signals. It also reports data parity errors via PERR# and address parity errors via SERR#.

Initiator State Machine

This block controls the PCI interface initiator functions. The states implemented are a subset of those defined in Appendix B of the PCI Local Bus Specification. The initiator control logic uses

DS206 August 31, 2005 | www.xilinx.com | 5 |

Product Specification v3.0.151 |

|

|