PCI32 Interface v3.0

Timing Specifications

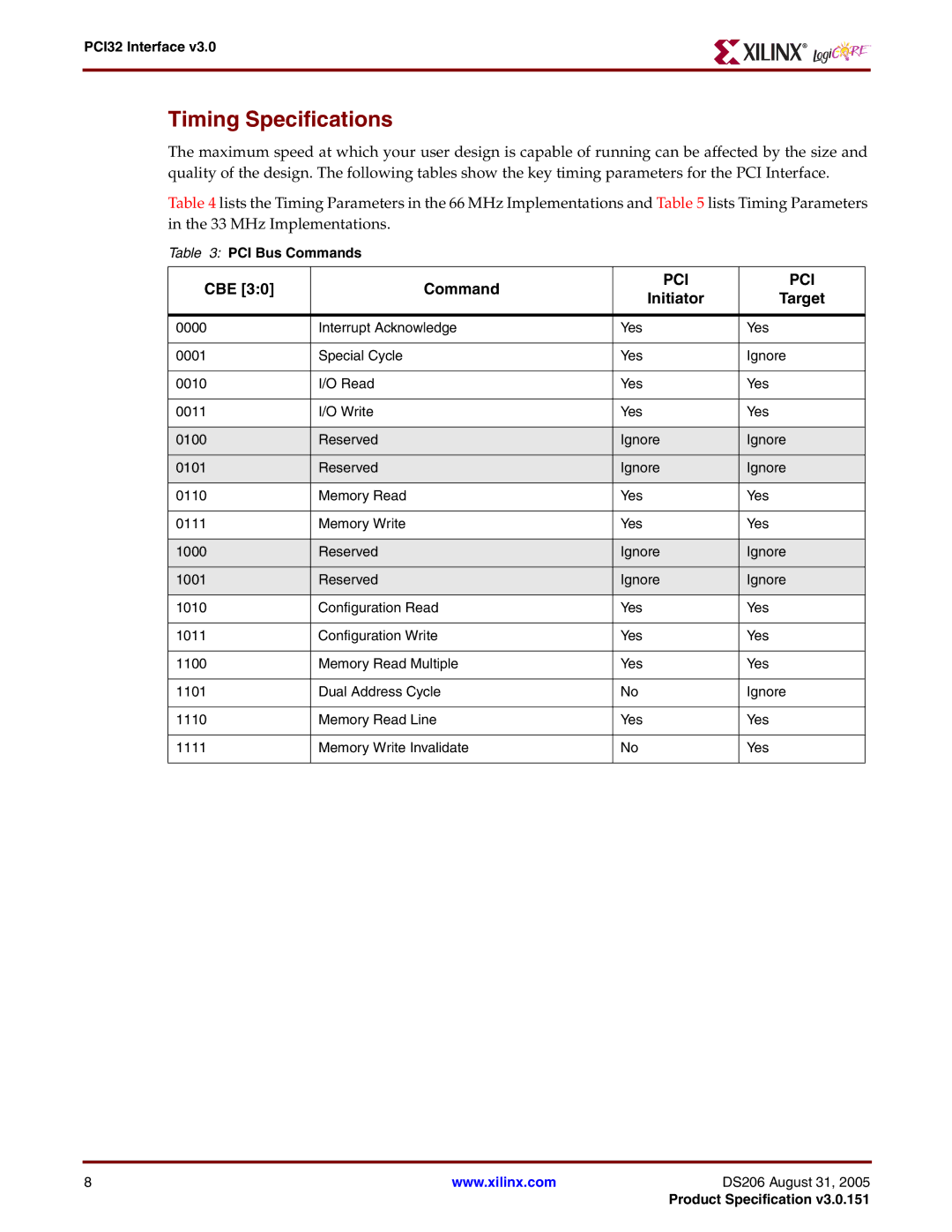

The maximum speed at which your user design is capable of running can be affected by the size and quality of the design. The following tables show the key timing parameters for the PCI Interface.

Table 4 lists the Timing Parameters in the 66 MHz Implementations and Table 5 lists Timing Parameters in the 33 MHz Implementations.

Table 3: PCI Bus Commands

CBE [3:0] | Command | PCI | PCI | |

Initiator | Target | |||

|

| |||

|

|

|

| |

0000 | Interrupt Acknowledge | Yes | Yes | |

|

|

|

| |

0001 | Special Cycle | Yes | Ignore | |

|

|

|

| |

0010 | I/O Read | Yes | Yes | |

|

|

|

| |

0011 | I/O Write | Yes | Yes | |

|

|

|

| |

0100 | Reserved | Ignore | Ignore | |

|

|

|

| |

0101 | Reserved | Ignore | Ignore | |

|

|

|

| |

0110 | Memory Read | Yes | Yes | |

|

|

|

| |

0111 | Memory Write | Yes | Yes | |

|

|

|

| |

1000 | Reserved | Ignore | Ignore | |

|

|

|

| |

1001 | Reserved | Ignore | Ignore | |

|

|

|

| |

1010 | Configuration Read | Yes | Yes | |

|

|

|

| |

1011 | Configuration Write | Yes | Yes | |

|

|

|

| |

1100 | Memory Read Multiple | Yes | Yes | |

|

|

|

| |

1101 | Dual Address Cycle | No | Ignore | |

|

|

|

| |

1110 | Memory Read Line | Yes | Yes | |

|

|

|

| |

1111 | Memory Write Invalidate | No | Yes | |

|

|

|

|

8 | www.xilinx.com | DS206 August 31, 2005 |

|

| Product Specification v3.0.151 |