PCI32 Interface v3.0

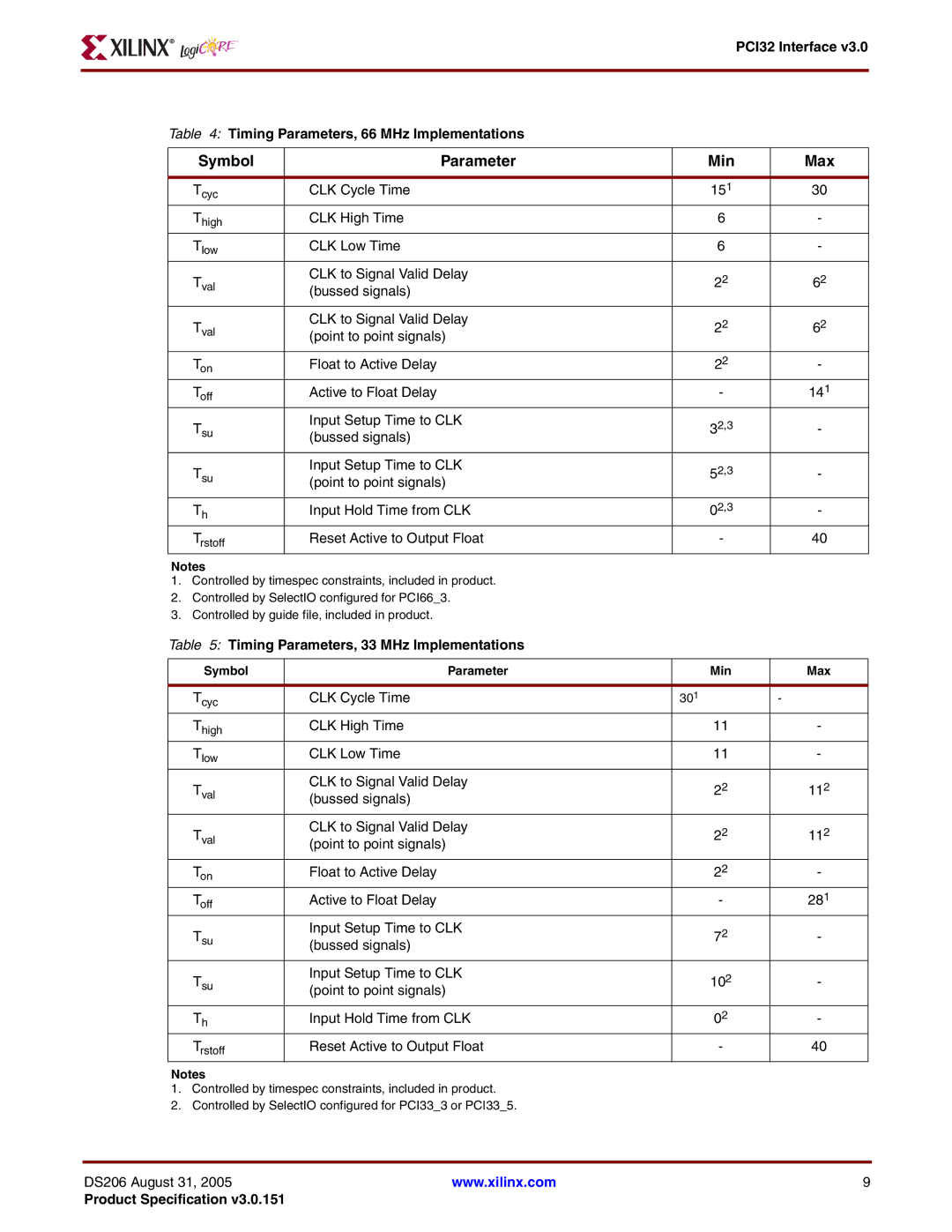

Table 4: Timing Parameters, 66 MHz Implementations

Symbol | Parameter | Min | Max | |

|

|

|

| |

T | CLK Cycle Time | 151 | 30 | |

cyc |

|

|

| |

Thigh | CLK High Time | 6 | - | |

Tlow | CLK Low Time | 6 | - | |

T | CLK to Signal Valid Delay | 22 | 62 | |

(bussed signals) | ||||

val |

|

| ||

|

|

|

| |

T | CLK to Signal Valid Delay | 22 | 62 | |

(point to point signals) | ||||

val |

|

| ||

|

|

|

| |

T | Float to Active Delay | 22 | - | |

on |

|

|

| |

T | Active to Float Delay | - | 141 | |

off |

|

|

| |

T | Input Setup Time to CLK | 32,3 | - | |

(bussed signals) | ||||

su |

|

| ||

|

|

|

| |

T | Input Setup Time to CLK | 52,3 | - | |

(point to point signals) | ||||

su |

|

| ||

|

|

|

| |

T | Input Hold Time from CLK | 02,3 | - | |

h |

|

|

| |

Trstoff | Reset Active to Output Float | - | 40 |

Notes

1.Controlled by timespec constraints, included in product.

2.Controlled by SelectIO configured for PCI66_3.

3.Controlled by guide file, included in product.

Table 5: Timing Parameters, 33 MHz Implementations

Symbol | Parameter | Min | Max | |

|

|

|

| |

T | CLK Cycle Time | 301 | - | |

cyc |

|

|

| |

Thigh | CLK High Time | 11 | - | |

Tlow | CLK Low Time | 11 | - | |

T | CLK to Signal Valid Delay | 22 | 112 | |

(bussed signals) | ||||

val |

|

| ||

|

|

|

| |

T | CLK to Signal Valid Delay | 22 | 112 | |

(point to point signals) | ||||

val |

|

| ||

|

|

|

| |

T | Float to Active Delay | 22 | - | |

on |

|

|

| |

T | Active to Float Delay | - | 281 | |

off |

|

|

| |

T | Input Setup Time to CLK | 72 | - | |

(bussed signals) | ||||

su |

|

| ||

|

|

|

| |

T | Input Setup Time to CLK | 102 | - | |

(point to point signals) | ||||

su |

|

| ||

|

|

|

| |

T | Input Hold Time from CLK | 02 | - | |

h |

|

|

| |

Trstoff | Reset Active to Output Float | - | 40 |

Notes

1.Controlled by timespec constraints, included in product.

2.Controlled by SelectIO configured for PCI33_3 or PCI33_5.

DS206 August 31, 2005 | www.xilinx.com | 9 |

Product Specification v3.0.151 |

|

|