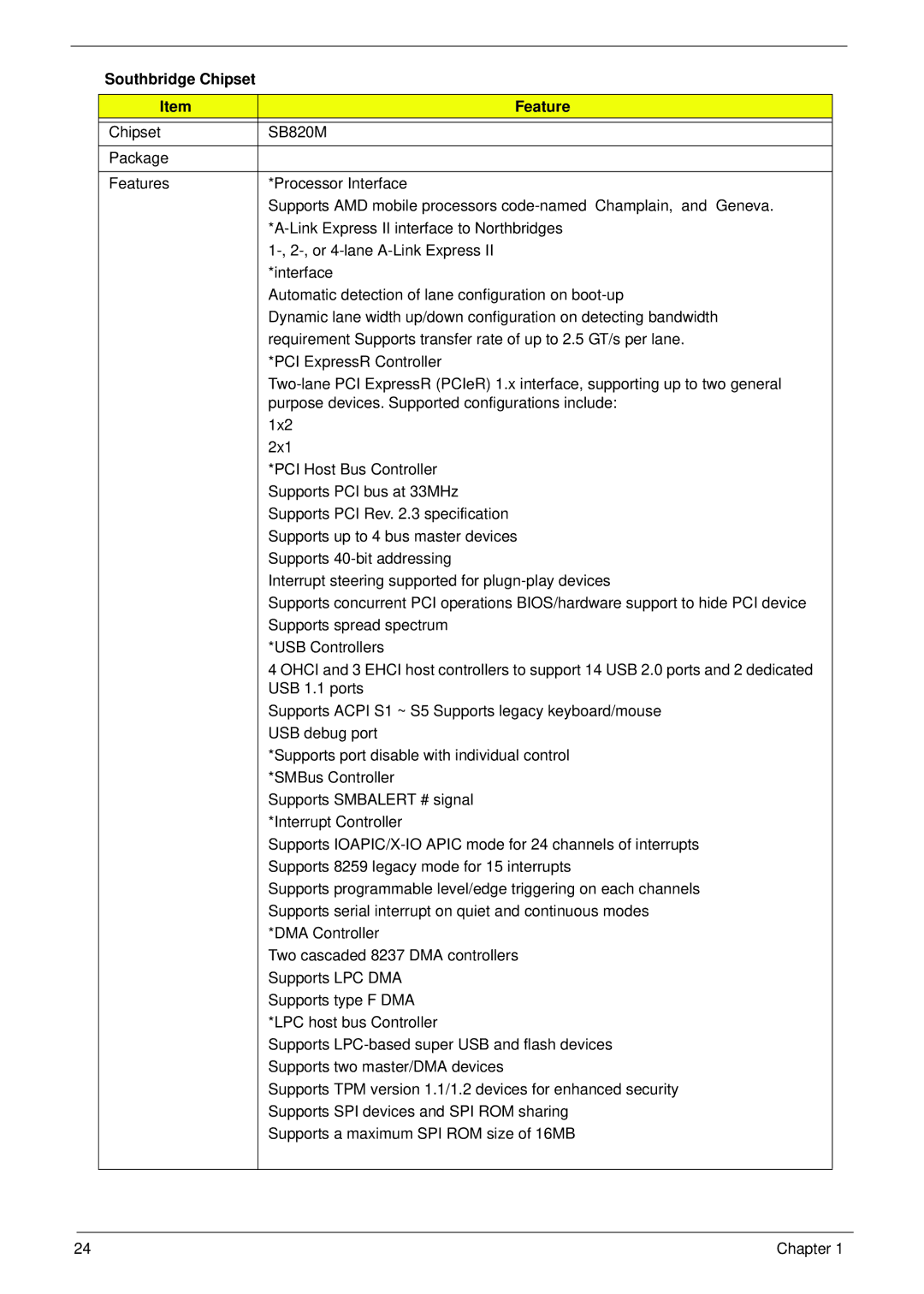

Southbridge Chipset

Item | Feature |

|

|

Chipset | SB820M |

Package |

|

|

|

Features | *Processor Interface |

| Supports AMD mobile processors |

| |

| |

| *interface |

| Automatic detection of lane configuration on |

| Dynamic lane width up/down configuration on detecting bandwidth |

| requirement Supports transfer rate of up to 2.5 GT/s per lane. |

| *PCI ExpressR Controller |

| |

| purpose devices. Supported configurations include: |

| 1x2 |

| 2x1 |

| *PCI Host Bus Controller |

| Supports PCI bus at 33MHz |

| Supports PCI Rev. 2.3 specification |

| Supports up to 4 bus master devices |

| Supports |

| Interrupt steering supported for |

| Supports concurrent PCI operations BIOS/hardware support to hide PCI device |

| Supports spread spectrum |

| *USB Controllers |

| 4 OHCI and 3 EHCI host controllers to support 14 USB 2.0 ports and 2 dedicated |

| USB 1.1 ports |

| Supports ACPI S1 ~ S5 Supports legacy keyboard/mouse |

| USB debug port |

| *Supports port disable with individual control |

| *SMBus Controller |

| Supports SMBALERT # signal |

| *Interrupt Controller |

| Supports |

| Supports 8259 legacy mode for 15 interrupts |

| Supports programmable level/edge triggering on each channels |

| Supports serial interrupt on quiet and continuous modes |

| *DMA Controller |

| Two cascaded 8237 DMA controllers |

| Supports LPC DMA |

| Supports type F DMA |

| *LPC host bus Controller |

| Supports |

| Supports two master/DMA devices |

| Supports TPM version 1.1/1.2 devices for enhanced security |

| Supports SPI devices and SPI ROM sharing |

| Supports a maximum SPI ROM size of 16MB |

|

|

24 | Chapter 1 |