System Architecture

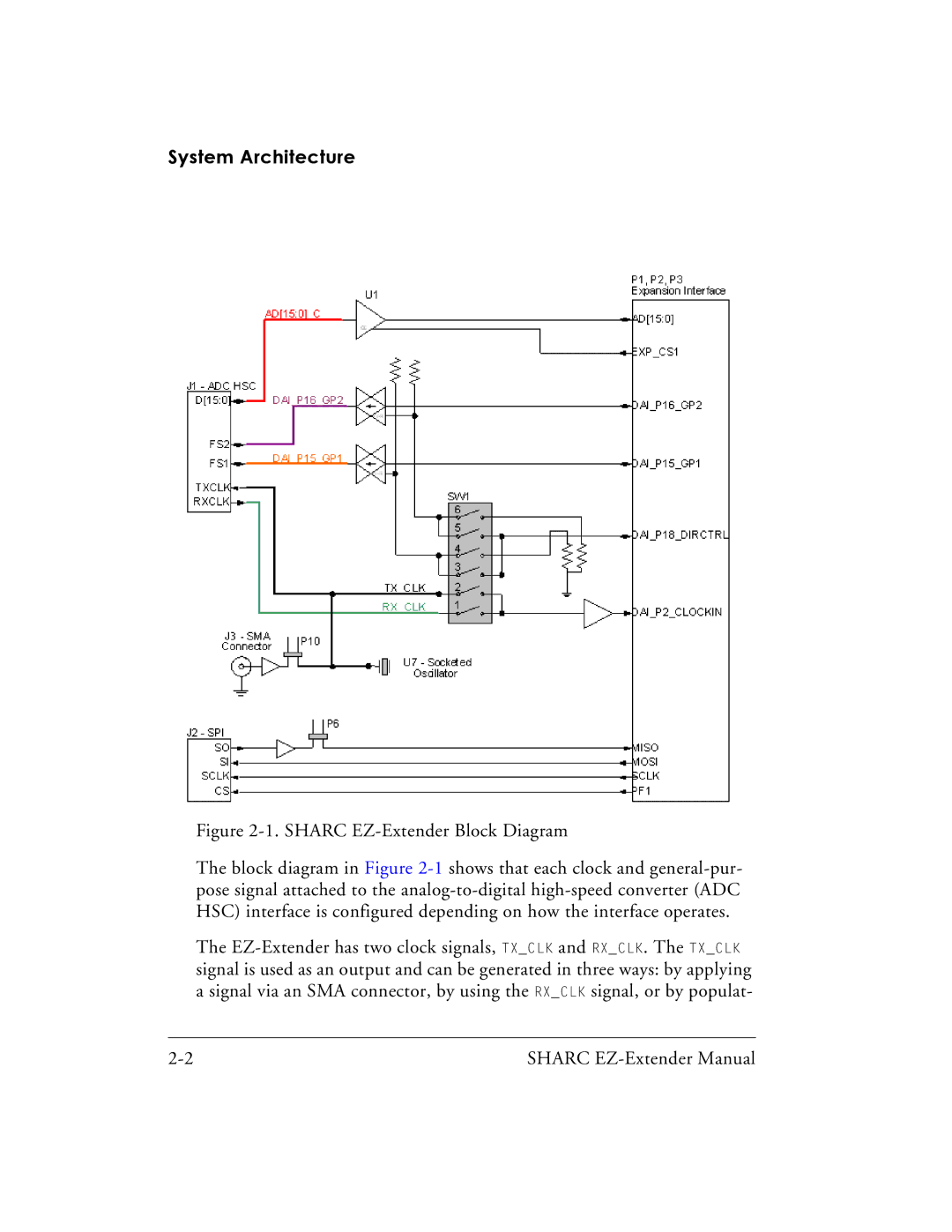

Figure 2-1. SHARC EZ-Extender Block Diagram

The block diagram in Figure 2-1shows that each clock and general-pur- pose signal attached to the analog-to-digital high-speed converter (ADC HSC) interface is configured depending on how the interface operates.

The EZ-Extender has two clock signals, TX_CLK and RX_CLK. The TX_CLK signal is used as an output and can be generated in three ways: by applying a signal via an SMA connector, by using the RX_CLK signal, or by populat-

2-2 | SHARC EZ-Extender Manual |