LDT

& PCI

& PCI

Bus Control

Bus Control

Advanced

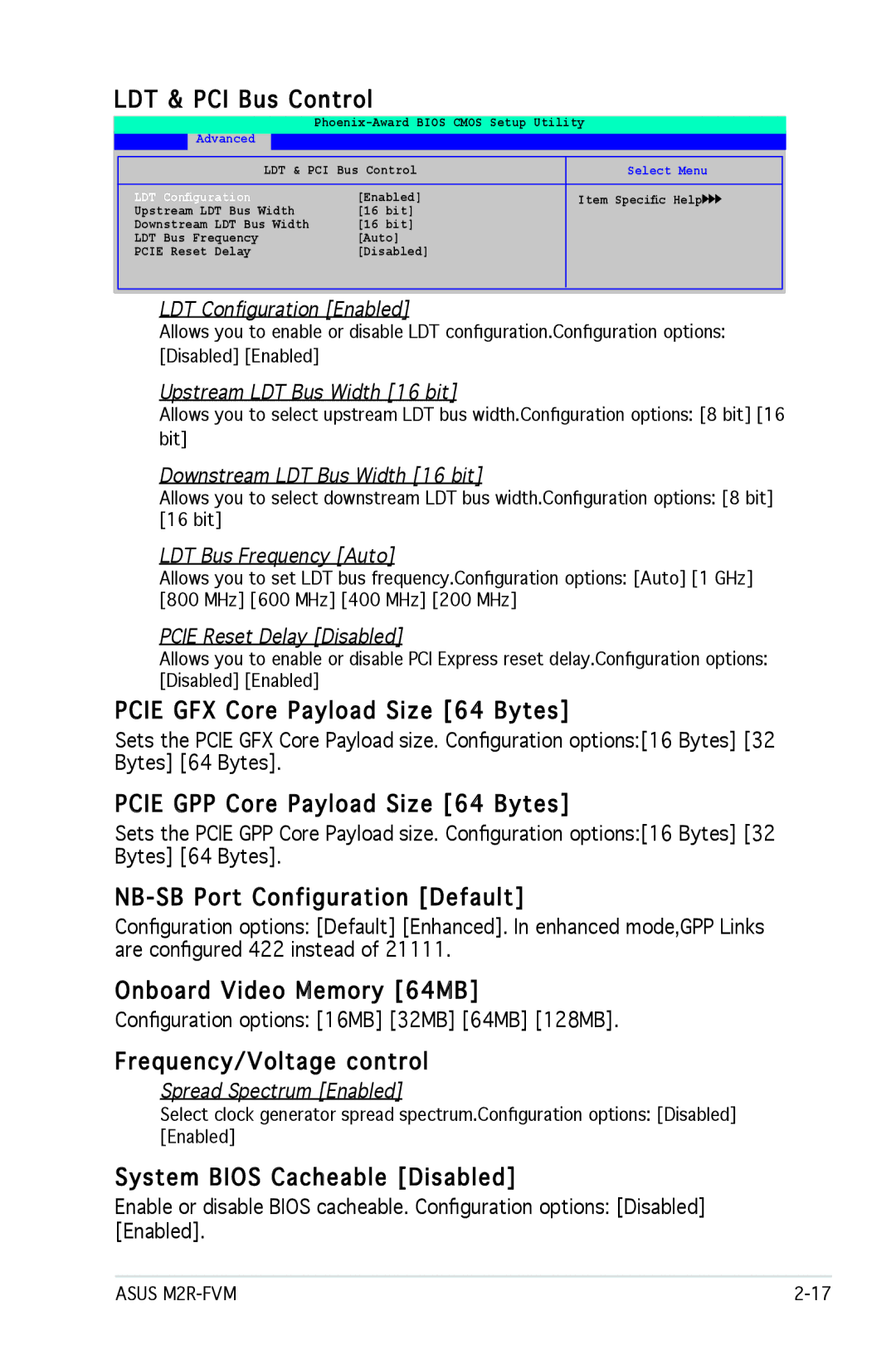

LDT & PCI Bus Control | Select Menu | ||

|

|

| |

LDT Configuration | [Enabled] | Item Specific Help | |

Upstream LDT Bus Width | [16 | bit] |

|

Downstream LDT Bus Width | [16 | bit] |

|

LDT Bus Frequency | [Auto] |

| |

PCIE Reset Delay | [Disabled] |

| |

|

|

|

|

LDT Configuration [Enabled]

Allows you to enable or disable LDT configuration.Configuration options: [Disabled] [Enabled]

Upstream LDT Bus Width [16 bit]

Allows you to select upstream LDT bus width.Configuration options: [8 bit] [16 bit]

Downstream LDT Bus Width [16 bit]

Allows you to select downstream LDT bus width.Configuration options: [8 bit] [16 bit]

LDT Bus Frequency [Auto]

Allows you to set LDT bus frequency.Configuration options: [Auto] [1 GHz] [800 MHz] [600 MHz] [400 MHz] [200 MHz]

PCIE Reset Delay [Disabled]

Allows you to enable or disable PCI Express reset delay.Configuration options: [Disabled] [Enabled]

PCIE

GFX Core Payload Size [64

GFX Core Payload Size [64

Bytes]

Bytes]

Sets the PCIE GFX Core Payload size. Configuration options:[16 Bytes] [32 Bytes] [64 Bytes].

PCIE

GPP Core Payload Size [64

GPP Core Payload Size [64

Bytes]

Bytes]

Sets the PCIE GPP Core Payload size. Configuration options:[16 Bytes] [32 Bytes] [64 Bytes].

NB-SB Port Configuration [Default]

Configuration options: [Default] [Enhanced]. In enhanced mode,GPP Links are configured 422 instead of 21111.

Onboard Video Memory [64MB]

Configuration options: [16MB] [32MB] [64MB] [128MB].

Frequency/Voltage

control

control

Spread Spectrum [Enabled]

Select clock generator spread spectrum.Configuration options: [Disabled] [Enabled]

System BIOS Cacheable [Disabled]

Enable or disable BIOS cacheable. Configuration options: [Disabled] [Enabled].

ASUS |