BUTTON MATRIX

| KI1 | KI2 | KI3 | KI4 | KI5 | |

|

|

|

|

|

| |

KO0 | 3 | 0 | 2 | 1 |

| |

|

|

|

|

|

| |

KO1 | Control | Demo | Effect | MIDI |

| |

|

|

|

|

|

| |

KO2 | + | 9 | 7 | 8 |

| |

|

|

|

|

|

| |

KO3 | 6 | - | 5 | 4 |

| |

|

|

|

|

|

| |

KO4 | Tone | MIDI | Channel | Octave | Modulation | |

Channel | On/Off | Shift | ||||

|

|

| ||||

|

|

|

|

|

|

POWER SUPPLY CIRCUIT

The power supply circuit generates six voltages as shown in the following table. VDD voltage is always generated. The others are controlled by APO signal output from the CPU.

Name | Voltage | For operation of |

|

|

|

VDD | +5 V | CPU, Reset IC, Working storage RAM |

|

|

|

DVDD | +5 V | DSP, Key touch LSI, Sound source ROM, Effect RAM, KO siginal generator |

|

|

|

AVDD | +5V | DAC, Filter |

|

|

|

LVDD | +4.5 V | LED Driver |

|

|

|

VCC | +9 V | Power amplifier, Pilot lamp |

|

|

|

VC | +9 V | Power amplifier |

|

|

|

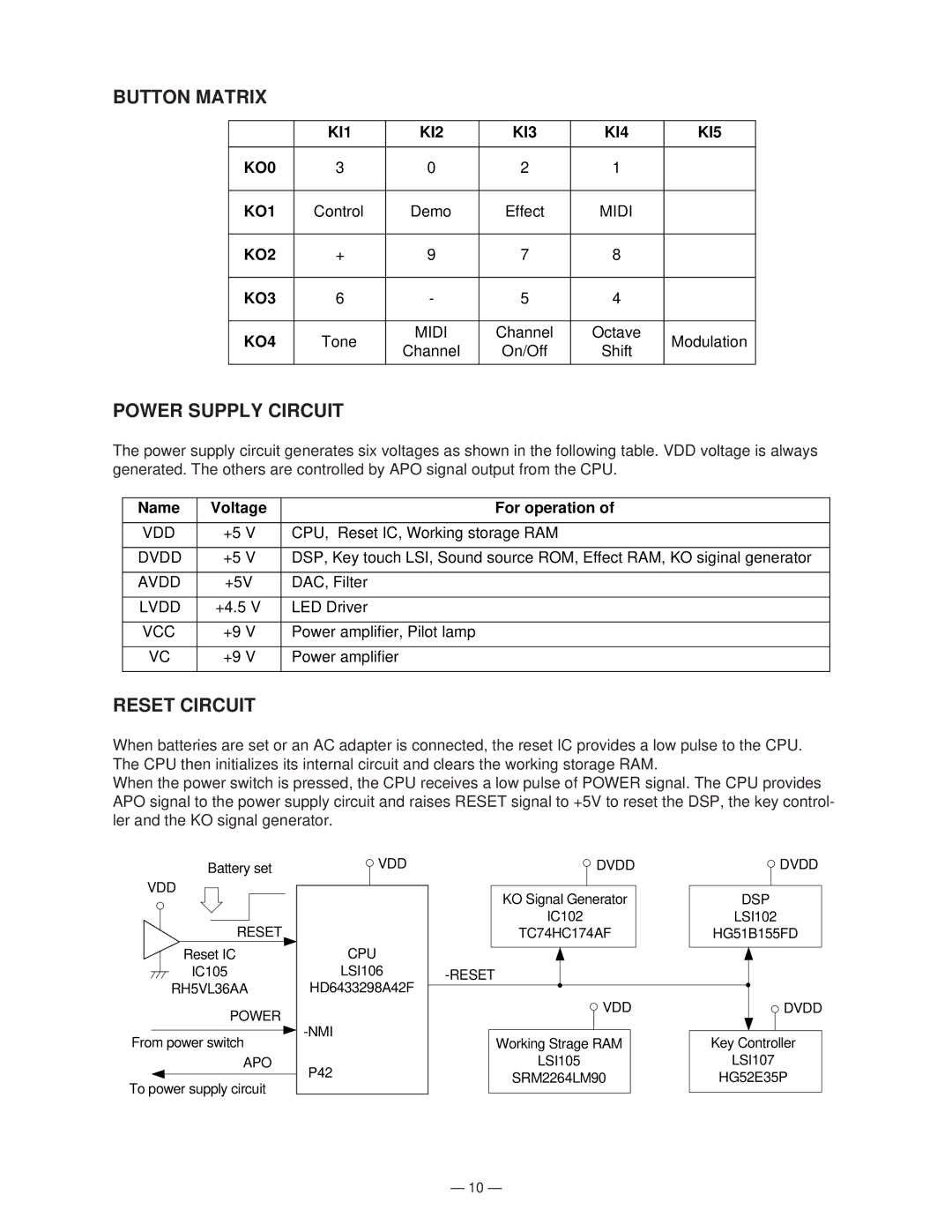

RESET CIRCUIT

When batteries are set or an AC adapter is connected, the reset IC provides a low pulse to the CPU. The CPU then initializes its internal circuit and clears the working storage RAM.

When the power switch is pressed, the CPU receives a low pulse of POWER signal. The CPU provides APO signal to the power supply circuit and raises RESET signal to +5V to reset the DSP, the key control- ler and the KO signal generator.

Battery set | VDD | |

| ||

VDD |

| |

RESET |

| |

Reset IC | CPU | |

IC105 | LSI106 | |

RH5VL36AA | HD6433298A42F | |

POWER | ||

From power switch | ||

| ||

APO | P42 | |

| ||

To power supply circuit |

|

| DVDD |

| DVDD | |

|

| |||

|

|

|

|

|

KO Signal Generator |

| DSP | ||

IC102 |

| LSI102 | ||

TC74HC174AF |

| HG51B155FD | ||

|

|

|

|

|

| VDD |

| DVDD | |

|

| |||

| ||||

|

|

|

|

|

Working Strage RAM |

| Key Controller | ||

LSI105 |

| LSI107 | ||

SRM2264LM90 |

| HG52E35P | ||

|

|

|

|

|

— 10 —