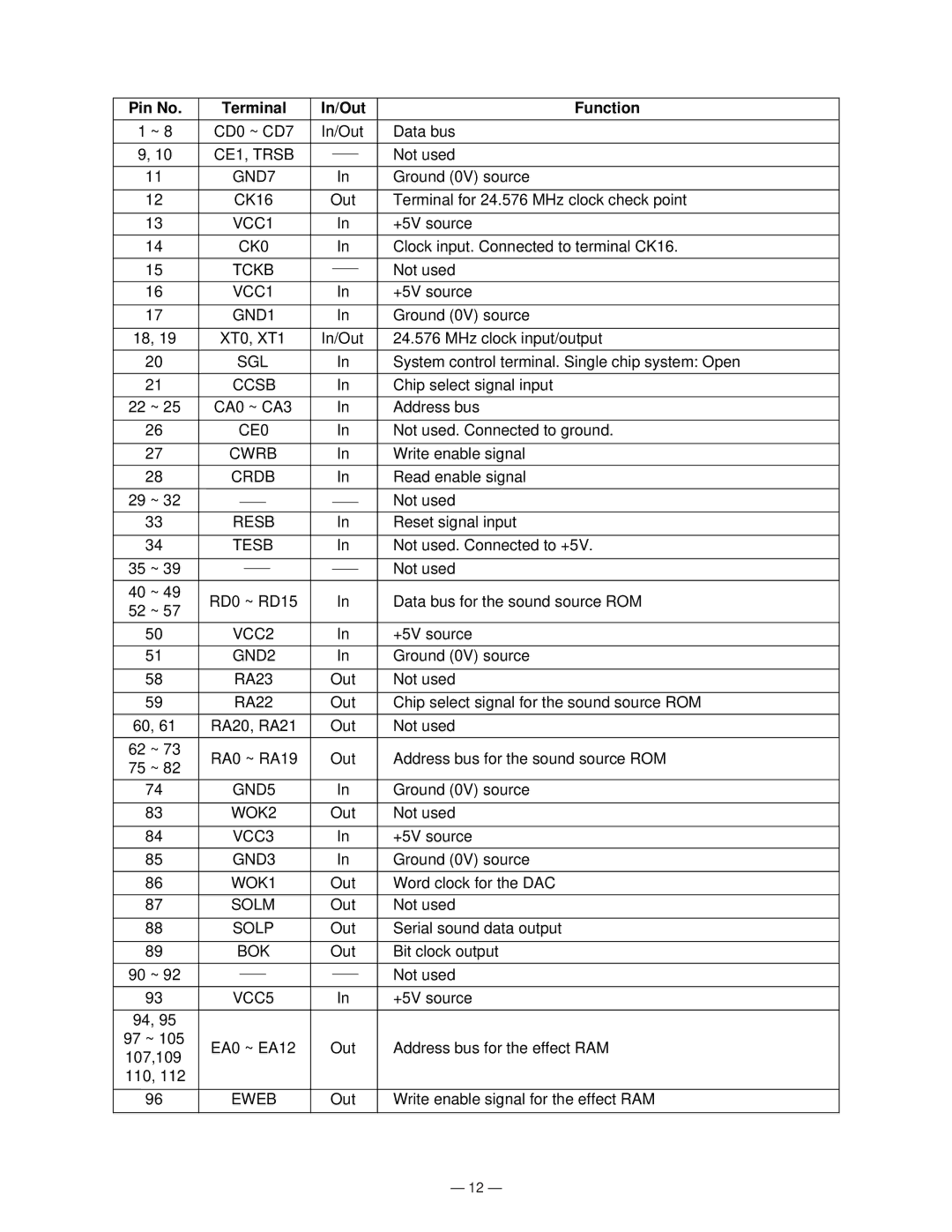

Pin No. | Terminal | In/Out | Function | |||||||

1 ~ 8 | CD0 ~ CD7 | In/Out | Data bus | |||||||

|

|

|

|

|

|

|

| |||

9, 10 | CE1, TRSB |

|

|

| Not used | |||||

|

|

| ||||||||

|

|

|

|

|

|

| ||||

11 | GND7 |

| In | Ground (0V) source | ||||||

|

|

|

|

|

| |||||

12 | CK16 | Out | Terminal for 24.576 MHz clock check point | |||||||

|

|

|

|

|

|

| ||||

13 | VCC1 |

| In | +5V source | ||||||

|

|

|

|

|

|

| ||||

14 | CK0 |

| In | Clock input. Connected to terminal CK16. | ||||||

|

|

|

|

|

|

|

| |||

15 | TCKB |

|

|

| Not used | |||||

|

|

| ||||||||

|

|

|

|

|

|

| ||||

16 | VCC1 |

| In | +5V source | ||||||

|

|

|

|

|

|

| ||||

17 | GND1 |

| In | Ground (0V) source | ||||||

|

|

|

|

|

| |||||

18, 19 | XT0, XT1 | In/Out | 24.576 MHz clock input/output | |||||||

|

|

|

|

|

|

| ||||

20 | SGL |

| In | System control terminal. Single chip system: Open | ||||||

|

|

|

|

|

|

| ||||

21 | CCSB |

| In | Chip select signal input | ||||||

|

|

|

|

|

|

| ||||

22 ~ 25 | CA0 ~ CA3 |

| In | Address bus | ||||||

|

|

|

|

|

|

| ||||

26 | CE0 |

| In | Not used. Connected to ground. | ||||||

|

|

|

|

|

|

| ||||

27 | CWRB |

| In | Write enable signal | ||||||

|

|

|

|

|

|

| ||||

28 | CRDB |

| In | Read enable signal | ||||||

|

|

|

|

|

|

|

|

|

| |

29 ~ 32 |

|

|

|

|

|

|

|

| Not used | |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

| ||||

33 | RESB |

| In | Reset signal input | ||||||

|

|

|

|

|

|

| ||||

34 | TESB |

| In | Not used. Connected to +5V. | ||||||

|

|

|

|

|

|

|

|

|

| |

35 ~ 39 |

|

|

|

|

|

|

|

| Not used | |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| |

40 ~ 49 | RD0 ~ RD15 |

| In | Data bus for the sound source ROM | ||||||

52 ~ 57 |

| |||||||||

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

| ||||

50 | VCC2 |

| In | +5V source | ||||||

|

|

|

|

|

|

| ||||

51 | GND2 |

| In | Ground (0V) source | ||||||

|

|

|

|

|

| |||||

58 | RA23 | Out | Not used | |||||||

|

|

|

|

|

| |||||

59 | RA22 | Out | Chip select signal for the sound source ROM | |||||||

|

|

|

|

|

| |||||

60, 61 | RA20, RA21 | Out | Not used | |||||||

|

|

|

|

|

|

|

|

|

| |

62 ~ 73 | RA0 ~ RA19 | Out | Address bus for the sound source ROM | |||||||

75 ~ 82 | ||||||||||

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

| ||||

74 | GND5 |

| In | Ground (0V) source | ||||||

|

|

|

|

|

| |||||

83 | WOK2 | Out | Not used | |||||||

|

|

|

|

|

|

| ||||

84 | VCC3 |

| In | +5V source | ||||||

|

|

|

|

|

|

| ||||

85 | GND3 |

| In | Ground (0V) source | ||||||

|

|

|

|

|

| |||||

86 | WOK1 | Out | Word clock for the DAC | |||||||

|

|

|

|

|

| |||||

87 | SOLM | Out | Not used | |||||||

|

|

|

|

|

| |||||

88 | SOLP | Out | Serial sound data output | |||||||

|

|

|

|

|

| |||||

89 | BOK | Out | Bit clock output | |||||||

|

|

|

|

|

|

|

|

|

| |

90 ~ 92 |

|

|

|

|

|

|

|

| Not used | |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

| ||||

93 | VCC5 |

| In | +5V source | ||||||

|

|

|

|

|

|

|

|

|

| |

94, 95 |

|

|

|

|

|

|

|

|

| |

97 ~ 105 | EA0 ~ EA12 | Out | Address bus for the effect RAM | |||||||

107,109 | ||||||||||

|

|

|

|

|

|

|

|

| ||

110, 112 |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

| |||||

96 | EWEB | Out | Write enable signal for the effect RAM | |||||||

|

|

|

|

|

|

|

|

|

| |

— 12 —