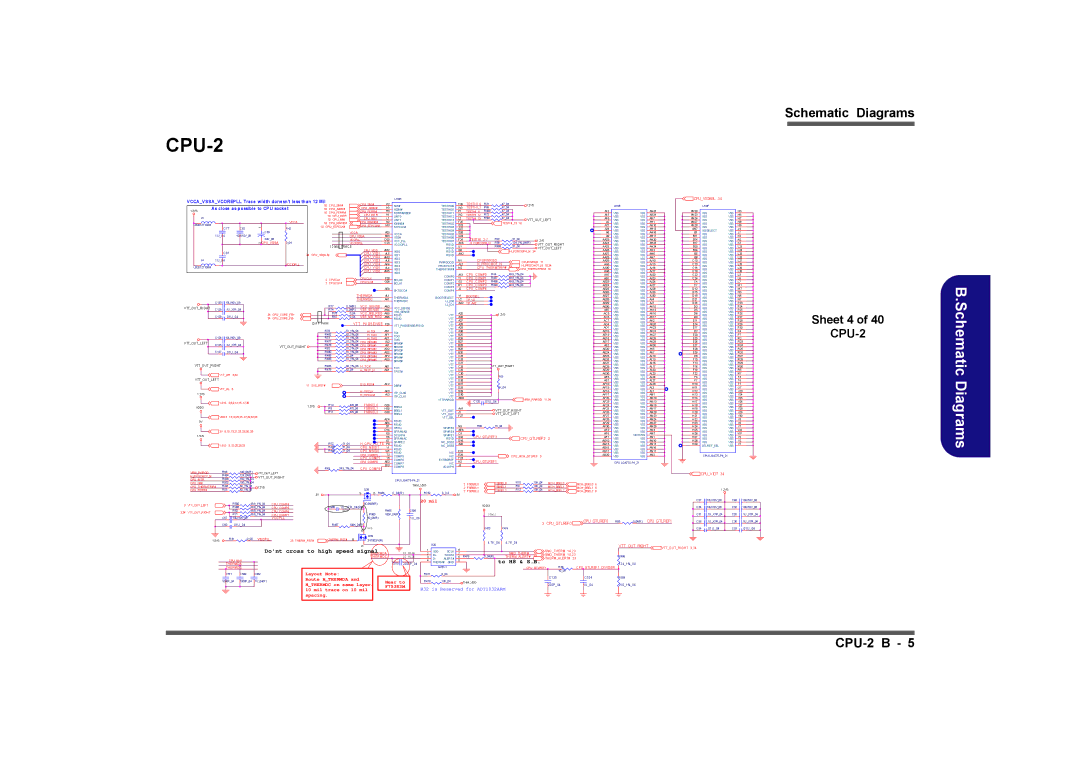

Schematic Diagrams

CPU-2

VCCA_VSSA_VCOREPLL Trace width donesn't less than 12 Mil |

|

|

|

|

| U19B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CPU_VIDSEL 34 |

|

| |||||||||

|

| CPU_SMI# | P2 |

|

|

|

|

| F26 | TESTHI_0 | R21 |

| 47_04 | 1.2VS |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

| 10 CPU_SMI# |

| SMI# |

|

|

| TESTHI00 |

|

|

|

|

| U19E |

|

|

|

|

| U19F |

|

| |||||||||||

| As close as possible to CPU socket |

| CPU_A20M# | K3 |

|

|

| W3 | TESTHI_1 | R69 |

| 47_04 |

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||

1.2VS | 10 CPU_A20M# |

| A20M# |

|

|

| TESTHI01 |

|

|

|

|

|

| A12 |

|

| AG23 |

|

| AN20 |

|

| H3 | ||||||||||||||||

|

|

|

|

|

|

| 10 CPU_FERR# |

| CPU_FERR# | R3 | FERR#/PBE# |

|

| TESTHI11 | P1 | TESTHI_11 | R493 |

| 47_04 |

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||

|

|

|

|

|

|

|

| 10 CPU_INTR |

|

| CPU_INTR | K1 | LINT0 |

|

|

| TESTHI12 | W2 | TESTHI_12 | R72 |

| 47_04 |

|

|

|

|

| A15 | VSS | VSS | AG24 |

|

| AN23 | VSS | VSS | H6 | ||

L5 |

|

|

|

|

|

|

|

|

| CPU_NMI | L1 |

|

|

| L2 | TESTHI_13 | R501 |

| 47_04 | VTT_OUT_LEFT |

|

| A18 | AG7 |

|

| AN24 | H7 | |||||||||||

|

|

|

|

|

|

| 10 CPU_NMI |

|

| LINT1 |

|

|

| TESTHI13 |

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||||||

LB2012T100M |

|

|

|

|

|

| VCCA | 10 CPU_IGNNE# |

| CPU_IGNNE# | N2 | IGNNE# |

|

| TESTHI02 | F25 |

|

|

| TESTHI_13 10 |

|

|

|

|

| A2 | VSS | VSS | AH1 |

|

| AN27 | VSS | VSS | H8 | ||||

|

|

|

|

|

|

|

| CPU_STPCLK# | M3 |

|

| G25 |

|

|

|

|

|

|

|

| A21 | AH10 |

|

| AN28 | H9 | |||||||||||||

| C77 | C82 | 1 |

| R42 | 10 CPU_STPCLK# |

| STPCLK# |

|

| TESTHI03 |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||

|

|

|

|

|

|

|

|

| G27 |

|

|

|

|

|

|

|

|

|

| A24 | AH13 |

|

| AN7 | J4 | ||||||||||||||

|

| + C83 |

|

|

|

|

|

|

|

|

|

|

| TESTHI04 |

|

|

|

|

|

|

|

|

| T | VSS | VSS |

|

| VIDSELECT | VSS | |||||||||

|

|

|

|

|

|

|

|

| VCCA |

|

| A23 |

|

|

|

| G26 |

|

|

|

|

|

|

|

|

| A6 | AH16 |

|

| B1 | J7 | |||||||

| 1U_04 | 10U/10V_08 |

|

|

|

|

|

| VCCA |

|

|

| TESTHI05 |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||

| 22U_08 |

|

|

| CPU_VSSA | B23 | VSSA |

|

|

| TESTHI06 | G24 | R22 |

| 51_04 |

|

|

|

|

| A9 | VSS | VSS | AH17 |

|

| B11 | VSS | VSS | K2 | |||||||||

|

|

|

|

|

|

|

| VCCPLL |

| D23 |

|

|

| F24 |

|

| 1.2VS |

|

|

| AA23 | AH20 |

|

| B14 | K5 | |||||||||||||

|

|

|

|

|

|

|

|

| VCC_PLL |

|

| TESTHI07 |

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||||||

|

|

|

|

| 2CPU_VSSA | 0_04 |

|

| VCCIOPLL |

| C23 |

|

| AK6 | H_FORCEPH_N | R56 |

| 124_1%_04(R) |

|

|

| AA24 | AH23 |

|

| B17 | K7 | ||||||||||||

|

|

|

|

|

|

|

| VCCIOPLL |

|

| RSVD |

| VTT_OUT_RIGHT |

| VSS | VSS |

|

| VSS | VSS | |||||||||||||||||||

|

|

|

|

|

|

|

| 12 MIL TRACE |

|

|

|

|

| U1 |

|

| R488 |

| 51_04 |

|

| AA25 | AH24 |

|

| B20 | L23 | ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RSVD |

|

|

|

| VTT_OUT_LEFT |

| VSS | VSS |

|

| VSS | VSS | ||||||||||||

|

| C61 |

|

|

|

|

|

|

|

| CPU_VID0 | AM2 | VID0 |

|

|

| RSVD | G6 |

|

|

|

| H_FORCEPH_N | 34 |

|

|

| AA26 | VSS | VSS | AH3 |

|

| B24 | VSS | VSS | L24 | ||

|

|

|

|

| 34 CPU_VID[0..6] |

|

|

| CPU_VID1 | AL5 |

|

|

| AH2 |

|

|

|

|

|

| AA27 | AH6 |

|

| B5 | L25 | |||||||||||||

|

|

|

|

|

|

|

| VID1 |

|

|

| RSVD |

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||

|

|

|

|

|

|

|

|

|

| CPU_VID2 | AM3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| AA28 | AH7 |

|

| B8 | L26 | ||||||||

L4 | 1U_04 |

|

|

|

|

|

|

|

|

| CPU_VID3 | AL6 | VID2 |

|

|

|

| N1 | CPUPWRGD |

| CPUPWRGD 11 |

|

|

| AA29 | VSS | VSS | AJ10 |

|

| C10 | VSS | VSS | L27 | |||||

|

|

|

|

|

|

|

|

| VID3 |

|

|

| PWRGOOD |

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||||||

|

|

|

|

|

|

| VCCIOPLL |

|

|

|

| CPU_VID4 | AK4 |

|

|

| AL2 | H_PROCHOT_N |

|

|

|

| AA3 | AJ13 |

|

| C13 | L28 | |||||||||||

|

|

|

|

|

|

|

|

|

|

| VID4 |

|

| PROCHOT# |

| H_PROCHOT_N | 10,34 |

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||||

LB2012T100M |

|

|

|

|

|

|

|

|

|

|

| CPU_VID5 | AL4 |

|

| M2 | CPU_THERMTRIP# |

|

| AA30 | AJ16 |

|

| C16 | L29 | ||||||||||||||

|

|

|

|

|

|

|

|

|

|

| VID5 |

|

| THERMTRIP# | CPU_THERMTRIP# 10 |

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| CPU_VID6 | AM5 |

|

|

|

|

|

|

|

|

| AA6 | AJ17 |

|

| C19 | L30 | |||||||||||

|

|

|

|

|

|

|

|

|

|

|

| VID6 |

|

|

|

|

| CPU_COMP0 | R44 |

| 49.9_1%_04 |

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| A13 |

|

|

|

|

|

| AA7 | AJ20 |

|

| C22 | L3 | |||||||||

|

|

|

|

|

|

|

| 2 CPUCLK |

| CPUCLK | F28 |

|

|

|

| COMP0 | T1 | CPU_COMP1 | R487 |

| 49.9_1%_04 |

|

|

|

|

| AB1 | VSS | VSS | AJ23 |

|

| C24 | VSS | VSS | L6 | |||

|

|

|

|

|

|

|

|

| BCLK0 |

|

|

| COMP1 |

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||||

|

|

|

|

|

|

|

|

| CPUCLK# | G28 |

|

|

| G2 | CPU_COMP2 | R498 |

| 49.9_1%_04 |

|

|

|

|

| AB23 | AJ24 |

|

| C4 | L7 | ||||||||||

|

|

|

|

|

|

|

| 2 CPUCLK# |

| BCLK1 |

|

|

| COMP2 |

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| R1 | CPU_COMP3 | R494 |

| 49.9_1%_04 |

|

|

|

|

| AB24 | AJ27 |

|

| C7 | M1 | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| COMP3 |

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| AE8 |

|

|

|

| J2 | CPU_COMP4 |

|

|

|

|

|

|

|

| AB25 | AJ28 |

|

| D12 | M7 | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

| SKTOCC# |

|

| COMP4 |

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| AB26 | AJ29 |

|

| D15 | N3 | |||||||

|

|

|

|

|

|

|

|

|

| THERMDA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||

|

|

|

|

|

|

|

|

|

| AL1 |

|

|

|

|

| Y1 | BOOTSEL |

|

|

|

|

|

|

|

|

| AB27 | AJ30 |

|

| D18 | N6 | |||||||

|

|

|

|

|

|

|

|

|

| THERMDA |

| BOOTSELECT |

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||

|

|

|

|

|

|

|

|

|

| THERMDC | AK1 |

| V2 | TP_V2 |

|

|

|

|

|

|

|

|

| AB28 | AJ4 |

|

| D21 | N7 | ||||||||||

| C133 | 10U/10V_08 |

|

|

|

|

| THERMDC |

|

| LL_ID0 |

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| AA2 | TP_AA2 |

|

|

|

|

|

|

|

|

| AB29 | AJ7 |

|

| D24 | P23 | |||||||||||

|

|

|

| R77 | 0_04(R) | VCC_SENSE |

|

|

|

|

| LL_ID1 |

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||

VTT_OUT_RI GHT |

|

|

|

|

|

|

| AN3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| AB30 | AK10 |

|

| D3 | P24 | ||||||||||

|

|

|

|

|

|

| VCC_SENSE |

|

|

|

|

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||

C129 | .1U_X7R_04 |

|

|

| R74 | 0_04(R) | VSS_SENSE | AN4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| AB7 | AK13 |

|

| D5 | P25 | |||||||||||

|

|

|

|

| 34 CPU_CORE_FB+ | R70 |

| 0_04 | VCC_MB_REG | AN5 | VSS_SENSE |

|

|

| A25 |

|

| 1.2VS |

|

|

|

|

|

| AC3 | VSS | VSS | AK16 |

|

| D6 | VSS | VSS | P26 | |||||

|

|

|

|

|

| RSVD |

|

|

| VTT |

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||||||||

| C128 | .01U_04 |

| R67 |

| 0_04 | VSS_MB_REG | AN6 |

|

|

| A26 |

|

|

|

|

|

|

|

| AC6 | AK17 |

|

| D9 | P27 | |||||||||||||

|

| 34 CPU_CORE_FB- |

| RSVD |

|

|

| VTT |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| A27 |

|

|

|

|

|

|

|

|

|

| AC7 | AK2 |

|

| E11 | P28 | |||||||||

|

|

|

|

|

|

| DIFF PAIR |

| VT T _ PK GS E NS E |

|

|

|

|

| VTT |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||

|

|

|

|

|

|

|

| F29 |

|

|

|

| A28 |

|

|

|

|

|

|

|

|

|

| AD4 | AK20 |

|

| E14 | P29 | ||||||||||

|

|

|

|

|

|

|

| VTT_PKGSENSE/RSVD |

| VTT |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| A29 |

|

|

|

|

|

|

|

|

|

| AD7 | AK23 |

|

| E17 | P30 | ||||||||

|

|

|

|

|

|

|

| R78 | 51_1%_04 |

|

|

|

|

|

|

| VTT |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||

|

|

|

|

|

|

|

|

| H_TDI | AD1 |

|

|

|

| A30 |

|

|

|

|

|

|

|

|

|

| AE10 | AK24 |

|

| E2 | P4 | ||||||||

|

|

|

|

|

|

|

|

| TDI |

|

|

| VTT |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||

|

|

|

|

|

|

|

| R482 | 62_1%_06 |

| H_TDO | AF1 |

|

|

| B25 |

|

|

|

|

|

|

|

|

|

| AE13 | AK27 |

|

| E20 | P7 | |||||||

|

|

|

|

|

|

|

|

| TDO |

|

|

| VTT |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||

| C126 | 10U/10V_08 |

|

|

| R73 | 51_1%_04 |

| H_TMS | AC1 |

|

|

| B26 |

|

|

|

|

|

|

|

|

|

| AE16 | AK28 |

|

| E25 | R2 | |||||||||

|

|

|

|

| TMS |

|

|

| VTT |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||||

VTT_OUT_LEFT |

|

|

|

|

|

|

| R477 | 51_1%_04 CPU_BPM#0 | AJ2 |

|

|

| B27 |

|

|

|

|

|

|

|

|

|

| AE17 | AK29 |

|

| E26 | R23 | |||||||||

|

|

|

|

|

|

| BPM0# |

|

| VTT |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||||||

C125 | .1U_X7R_04 |

| VTT_OUT_RIGHT | R478 | 51_1%_04 CPU_BPM#1 | AJ1 |

|

| B28 |

|

|

|

|

|

|

|

|

|

| AE2 | AK30 |

|

| E27 | R24 | ||||||||||||||

|

|

|

|

|

| R82 | 51_1%_04 CPU_BPM#2 | AD2 | BPM1# |

|

| VTT | B29 |

|

|

|

|

|

|

|

|

|

| AE20 | VSS | VSS | AK5 |

|

| E28 | VSS | VSS | R25 | ||||||

|

| .01U_04 |

|

|

|

| BPM2# |

|

| VTT |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||||||

| C127 |

|

|

|

| R480 | 51_1%_04 CPU_BPM#3 | AG2 |

|

| B30 |

|

|

|

|

|

|

|

|

|

| AE24 | AK7 |

|

| E29 | R26 | ||||||||||||

|

|

|

|

| BPM3# |

|

| VTT |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

| T | VSS | VSS | |||||||||||||||

|

|

|

|

|

|

|

| R486 | 51_04 | CPU_BPM#4 | AF2 |

|

| C25 |

|

|

|

|

|

|

|

|

|

| AE25 | AL10 |

| E8 | R27 | ||||||||||

|

|

|

|

|

|

|

| BPM4# |

|

| VTT |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||

|

|

|

|

|

|

|

| R483 | 51_1%_04 CPU_BPM#5 | AG3 |

|

| C26 |

|

|

|

|

|

|

|

|

|

| AE26 | AL13 |

|

| F10 | R28 | ||||||||||

|

|

|

|

|

|

|

| BPM5# |

|

| VTT |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C27 |

|

|

|

|

|

|

|

|

|

| AE27 | AL16 |

|

| F13 | R29 | |||||||

VTT_OUT_RIGHT |

|

|

|

|

|

| R485 | 62_1%_06 H_TCK |

|

|

|

|

| VTT |

|

| VTT_OUT_RIGHT |

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||||

|

|

|

|

|

| AE1 | TCK |

|

|

| C28 |

|

|

|

|

|

|

| AE28 | AL17 |

|

| F16 | R30 | |||||||||||||||

|

|

|

|

|

|

|

| R479 | 62_04 | H_TRST_N | AG1 |

|

|

| VTT | C29 |

|

|

|

|

|

|

|

|

|

| AE29 | VSS | VSS | AL20 |

|

| F19 | VSS | VSS | R5 | |||

|

|

|

|

|

|

|

| TRST# |

|

| VTT |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||

| VTT_OR 3,34 |

|

|

|

|

|

|

|

|

|

|

|

| C30 |

|

|

|

|

|

|

|

|

|

| AE30 | AL23 |

|

| F22 | R7 | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| VTT |

|

| R63 |

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| D25 |

|

|

|

|

|

|

|

| AE5 | AL24 |

|

| F4 | T3 | ||||||||||

VTT_OUT_LEFT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| VTT |

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| D26 |

|

|

|

|

|

|

|

|

|

| AE7 | AL27 |

|

| F7 | T6 | |||||||

|

|

|

|

|

|

| 11 SYS_RST# |

|

| SYS_RST# | AC2 |

|

|

|

| VTT | D27 |

|

|

|

|

|

|

|

|

|

| AF10 | VSS | VSS | AL28 |

|

| H10 | VSS | VSS | T7 | ||

|

|

|

|

|

|

|

|

| DBR# |

|

|

| VTT |

|

| 1K_04 |

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||||

| VTT_OL 3 |

|

|

|

|

|

|

|

|

|

|

| D28 |

|

|

|

|

|

|

|

| AF13 | AL3 |

|

| H11 | U7 | ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| VTT |

|

|

|

|

|

|

|

| VSS | VSS | T |

| VSS | VSS | ||||||||||

|

|

|

|

|

|

|

| H_ITPCLK | AK3 |

|

|

|

| D29 |

|

|

|

|

|

|

|

|

|

| AF16 | AL7 |

| H12 | V23 | ||||||||||

1.2VS |

|

|

|

|

|

|

|

| T |

| ITP_CLK0 |

|

| VTT |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||

|

|

|

|

|

|

|

|

| H_ITPCLK# | AJ3 |

|

| D30 |

|

|

|

|

|

|

|

|

|

| AF17 | AM1 |

|

| H13 | V24 | ||||||||||

|

|

|

|

|

|

|

| T |

| ITP_CLK1 |

|

| VTT |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| AM6 |

|

|

|

| VRM_PWRGD 11,34 |

|

| AF20 | AM10 |

|

| H14 | V25 | |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| VTTPWRGD | .01U_04 |

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||||

| 1.2VS | 5,6,9,12,15..17,30 |

|

|

|

|

|

|

|

|

|

|

|

|

| C120 |

|

|

|

| AF23 | AM13 |

|

| H17 | V26 | |||||||||||||

|

|

|

| R14 |

| 470_06 |

| FSBSEL0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||||

|

|

| 1.2VS |

|

| G29 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| AF24 | AM16 |

|

| H18 | V27 | |||||||||||

VDD3 |

|

|

|

|

|

|

|

| BSEL0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||

|

|

|

|

|

|

| R8 |

| 470_06 |

| FSBSEL1 | H30 |

|

|

|

| AA1 |

|

| VTT_OUT_RIGHT |

|

|

|

|

| AF25 | AM17 |

|

| H19 | V28 | ||||||||

|

|

|

|

|

|

|

|

|

| BSEL1 |

|

|

| VTT_OUT |

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||

|

|

|

|

|

|

|

| R11 |

| 470_06 |

| FSBSEL2 | G30 |

|

|

| J1 |

|

|

|

|

|

|

| AF26 | AM20 |

|

| H20 | V29 | |||||||||

|

|

|

|

|

|

|

|

|

| BSEL2 |

|

|

| VTT_OUT |

|

| VTT_OUT_LEFT |

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||||

| VDD3 | 13,19,23,25..27,29,32,33 |

|

|

|

|

|

|

|

|

|

|

| F27 |

|

|

|

|

|

|

| AF27 | AM23 |

|

| H21 | V30 | ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| VTT_SEL |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||

|

|

|

|

|

|

|

| AC4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| AF28 | AM24 |

|

| H22 | V3 | ||||||||||

3V |

|

|

|

|

|

|

|

|

|

|

|

| RSVD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||

|

|

|

|

|

|

|

|

|

|

|

| AE4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| AF29 | AM27 |

|

| H23 | V6 | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

| RSVD |

|

|

|

|

| R60 | 1K_04 |

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

| D1 |

|

|

|

| N5 |

|

|

|

|

|

| AF30 | AM28 |

|

| H24 | V7 | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| HFPLL |

|

|

| SPARE0 |

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||

| 3V 6,10..13,21,25..28,30..33 |

|

|

|

|

|

|

|

| D14 |

|

|

| AE6 |

|

|

|

|

|

|

|

|

|

| AF3 | AM4 |

|

| H25 | W4 | |||||||||

|

|

|

|

|

|

|

|

| SFRANAD |

|

| SPARE4 |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||||

|

|

|

|

|

|

|

|

| E5 |

|

| C9 |

|

|

|

|

|

|

|

|

|

| AF6 | AM7 |

|

| H26 | W7 | |||||||||||

1.5VS |

|

|

|

|

|

|

|

|

|

|

|

| DCLKPH |

|

| SPARE1 | CPU_GTLREF3 |

|

|

|

|

|

|

| VSS | VID7/VSS |

|

| VSS | VSS | |||||||||

|

|

|

|

|

|

|

|

|

|

|

| E6 |

|

| G10 |

| CPU_GTLREF3 3 |

|

| AF7 | AN1 |

|

| H27 | Y2 | ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| SFRANAC |

|

| RSVD |

|

|

| VSS | VSS |

|

| VSS | VSS | ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| E7 |

|

| D16 |

|

|

|

|

|

| AG10 | AN10 |

|

| H28 | Y5 | |||||||||||

|

|

|

|

|

|

|

| R57 | 51_04 | H_CPU_PD_F6 | SPARE2 |

|

| NC_DSS2 |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

| VSS | VSS | |||||||||

| 1.5VS | 9..13,25,28,33 |

|

|

| F6 |

|

| A20 |

|

|

|

|

|

|

|

|

|

| AG13 | AN13 |

|

| H29 | Y7 | ||||||||||||||

|

|

|

| RSVD |

|

|

| NC_DSS3 |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

| T | GTLREF_SEL | VSS | |||||||||||||||

|

|

|

| R490 | 51_04 | CPU_MSID1 | V1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| AG16 | AN16 |

|

|

| |||||||||||||

|

|

|

|

|

|

|

| RSVD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

| R489 | 51_04 | CPU_MSID0 | W1 |

|

|

|

| E23 |

|

|

|

|

|

|

|

|

|

| AG17 | AN17 |

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

| RSVD |

|

|

| NC |

|

|

|

|

|

|

|

|

|

| VSS | VSS |

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

| CPU_COMP5 | T2 |

|

|

| E24 |

|

|

|

|

|

|

|

|

|

| AG20 | AN2 |

|

|

| CPU |

|

| |||||

|

|

|

|

|

|

|

|

|

|

| COMP5 |

|

| NC |

|

|

|

| CPU_MCH_GTLREF 5 |

|

|

| VSS | VSS |

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

| CPU_COMP7 | Y3 |

|

| F23 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

| COMP6 |

|

| EXTBGREF | CPU_GTLREF1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

| CPU_COMP6 | AE3 |

|

| H2 |

|

|

|

|

|

|

|

| CPU |

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

| COMP7 |

|

| NC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| B13 |

|

| J3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

| R43 | 24.9_1%_04 | CPU_COMP8 | COMP8 |

|

| ACLKPH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

| R66 |

| 100_04(R) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

VRM_PWRGD |

|

| VTT_OUT_LEFT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CPU_VID7 34 |

|

| ||||

| R464 | 124_04(R) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

H_PROCHOT_N | VTT_OUT_RIGHT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

CPU_INTR |

| R499 | 150_1%_04 |

|

|

|

|

|

|

| CPU |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

CPU_NMI |

| R502 | 150_1%_04 |

|

|

|

|

|

|

|

|

|

| THM_VDD |

|

|

| 2 FSBSEL0 |

| FSBSEL0 | R15 |

| 10K_04 MCH_BSEL0 | MCH_BSEL0 6 |

|

|

|

|

|

|

|

|

|

| |||||

CPU_THERMTRIP# | R491 | 62_1%_06 | 1.2VS |

|

|

|

|

|

|

|

|

|

|

|

| 2 FSBSEL1 |

| FSBSEL1 | R9 |

| 10K_04 | MCH_BSEL1 | MCH_BSEL1 6 |

|

|

|

|

|

|

|

|

|

| ||||||

CPU_FERR# |

| R55 |

| 62_1%_06 |

|

|

|

|

|

| S | Q38 |

| 0_04(R) | R732 |

| 0_04 |

| 2 FSBSEL2 |

| FSBSEL2 | R12 |

| 10K_04 | MCH_BSEL2 | MCH_BSEL2 6 |

|

|

|

|

|

|

| 1.2VS |

| ||||

|

|

|

|

|

|

|

| 3V |

|

| D R466 |

| 3V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

| R500 | 49.9_1%_04 |

|

|

|

|

|

| AO3409(R) |

|

|

| 20 mil |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C57 | 10U/10V_08 | C48 | 10U/10V_08 | ||

3 VTT_OUT_LEFT |

|

| CPU_COMP4 |

| .1U_X7R_04(R)G |

|

|

|

|

|

| VDD3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

| R495 | 49.9_1%_04 | CPU_COMP5 | C988 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C34 | 10U/10V_08 | C32 | 10U/10V_08 | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

3,34 VTT_OUT_RIGHT |

|

| R62 | 49.9_1%_04 CPU_COMP6 |

| D05 |

|

| R860 | R465 |

| C506 |

|

|

|

|

| 10mil |

|

|

|

|

|

|

|

|

|

|

|

|

| C31 | .1U_X7R_04 | C55 | .1U_X7R_04 | ||||

|

|

| R71 | 49.9_1%_04 CPU_COMP7 |

|

|

|

| 100K_04(R) | 1U_06 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

| C67 | 10U/10V_08 |

| VCCPLL |

|

|

|

|

| 10_04(R) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CPU_GTLREF0 | R85 | 0_04(R) | CPU_GTLREF1 |

| C58 | .1U_X7R_04 | C36 | .1U_X7R_04 | ||||

|

| C60 | .01U_04 |

|

|

| R467 |

| 100K_04(R) |

|

|

|

|

|

|

|

|

|

|

|

|

| 3 CPU_GTLREF0 |

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

| D | D05 |

|

|

|

|

|

|

|

| R475 |

| R474 |

|

|

|

|

|

|

|

|

|

|

|

| C54 | .01U_04 | C53 | .01U_04 |

|

|

| R41 | 0_06 | VCCPLL |

|

| THERM_RST# | G |

| Q39 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| 1.5VS |

|

| 23 THERM_RST# |

| 2N7002W(R) |

|

|

|

|

|

|

|

| 4.7K_04 | 4.7K_04 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

| S |

|

|

|

|

| U20 |

|

|

|

|

|

|

|

|

| VTT_OUT_RIGHT |

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| VTT_OUT_RIGHT 3,34 |

|

|

| |||||||

|

|

|

|

| Do'nt cross to high speed signal |

|

| 10 MILE | 1 | D+ | SDATA | 8 |

|

|

|

|

|

|

| SMD_THERM 14,23 |

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

| THERMDA |

|

| VDD | SCLK |

|

|

|

| SMD_THERM |

| SMC_THERM 14,23 |

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2 | 7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

| THERMDA |

|

|

|

|

|

|

| THERMDC | C510 | 10 MILE | 3 | D- | ALERT# | 6 R476 | 0_04(R) | THERM_ALERT# |

| THERM_ALERT# 23 |

|

| R496 |

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

| 2200P_04 | 4 | THERM# GND | 5 |

|

| to H8 & S.B. |

|

|

|

| 124_1%_04 |

|

|

|

|

|

|

| ||||||||||

|

|

| CPU_NMI |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

| THERMDC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CPU_GTLREF1 | R86 | CPU_GTLREF1_DIVIDER |

|

|

|

|

|

|

|

| ||||||||

|

| C511 | C509 | C982 |

| Layout Note: |

|

|

|

|

|

| R471 |

| 0_04 |

|

|

|

|

|

|

|

|

| 10_04 |

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C130 |

| C524 |

| R504 |

|

|

|

|

|

|

|

| |||||||||

|

| 1000P_04 | 1000P_04 | .1U_04(R) |

| Route H_THERMDA and |

|

| Near to | R470 |

| 10K_04 | THM_VDD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

| H_THERMDC on same layer. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

| F75383M | R32 is Reserved for ADT1032ARM |

|

|

| 220P_04 | 1U_04 |

| 210_1%_06 |

|

|

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

| 10 mil trace on 10 mil |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

| spacing. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

Sheet 4 of 40

CPU-2

![]() B.Schematic Diagrams

B.Schematic Diagrams