CY62128B specifications

The Cypress CY62128B is a high-performance static random-access memory (SRAM) device designed to deliver reliable data storage solutions in a variety of applications. This device is particularly notable for its speed and high-density capabilities, making it suitable for both consumer electronics and industrial applications.One of the main features of the CY62128B is its organization as a 128K-bit memory chip, which typically comes in a 16K x 8-bit configuration. This allows for efficient processing and storage of data, enabling quick access times. The device boasts access times of 55 ns, making it an excellent choice for applications that require fast data retrieval and processing. Such speed is crucial for modern computing tasks, where delays can significantly impact overall performance.

In addition to its speed, the CY62128B incorporates low-power consumption technology, which is vital for battery-operated devices and other energy-sensitive applications. The operating current is typically in the range of 30 mA, while the standby current is a mere 0.02 mA when the chip is not in use. This combination of low power and high-speed functionality ensures that the device operates efficiently in a wide range of conditions.

The CY62128B also features a wide operating voltage range, accommodating both 2.7V to 5.5V. This versatility allows it to be employed in diverse environments and devices, adapting as necessary to various power supply configurations. Its compatibility with different voltage levels enhances its usability in portable electronics and various embedded systems.

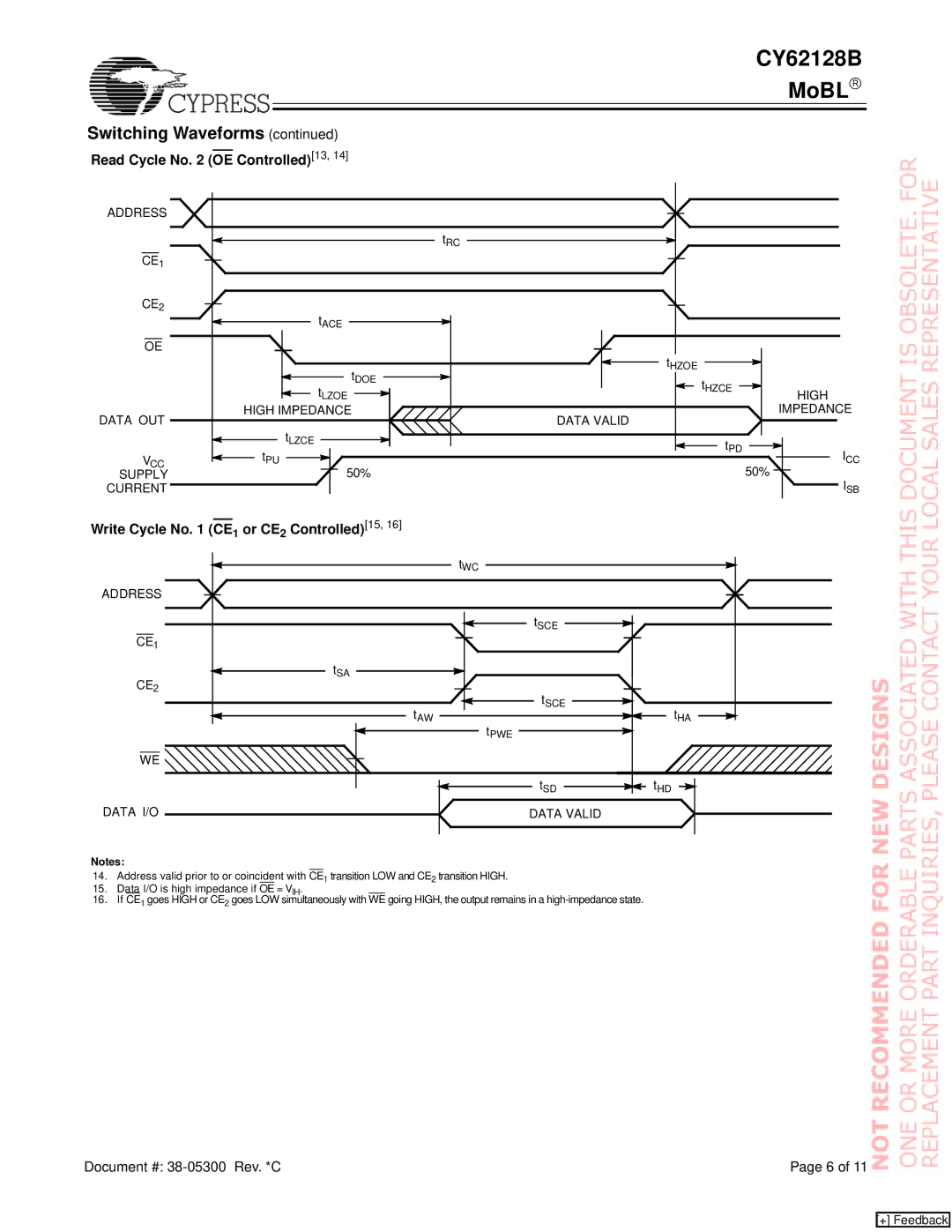

Additionally, the CY62128B benefits from a fast transition between read and write operations, thanks to its asynchronous memory structure. This means that data can be changed and accessed without the need for complex timing sequences, promoting simplicity in system design and reducing overhead.

Another significant characteristic is the robust reliability of the CY62128B, which uses advanced CMOS technology. The chip is built to withstand challenging operating conditions, such as extreme temperatures and radiation exposure, making it suitable for aerospace and military applications.

In summary, the Cypress CY62128B is a versatile and reliable SRAM solution, offering high density, fast access times, low power consumption, and a broad operating voltage range. These features make it an ideal choice for diverse applications, from consumer electronics to industrial systems. Its combination of speed, efficiency, and reliability reflects the innovation that Cypress is known for in the semiconductor industry.