CY7C1307BV25, CY7C1305BV25 specifications

Cypress Semiconductor, a leader in embedded memory solutions, includes the CY7C1305BV25 and CY7C1307BV25 in its family of high-performance synchronous dynamic random-access memory (SDRAM) devices. These memory chips are designed for applications that require high-speed data processing and low power consumption, making them ideal for communication systems, networking devices, and other consumer electronics.The CY7C1305BV25 is a 512K x 16-bit synchronous SRAM, while the CY7C1307BV25 offers a larger capacity of 1M x 16-bit. Both chips operate at a maximum clock frequency of 166 MHz, ensuring rapid data transfer rates and efficient memory operation. This high-speed performance is crucial in applications where quick data retrieval and storage are imperative.

One of the standout features of these devices is their ability to support a wide range of operating voltages, typically from 2.5V to 3.3V. This versatility allows them to be integrated into systems with varying power requirements, enhancing their adaptability for different designs. Additionally, the chips offer a low standby power consumption level, contributing to energy efficiency in battery-operated devices.

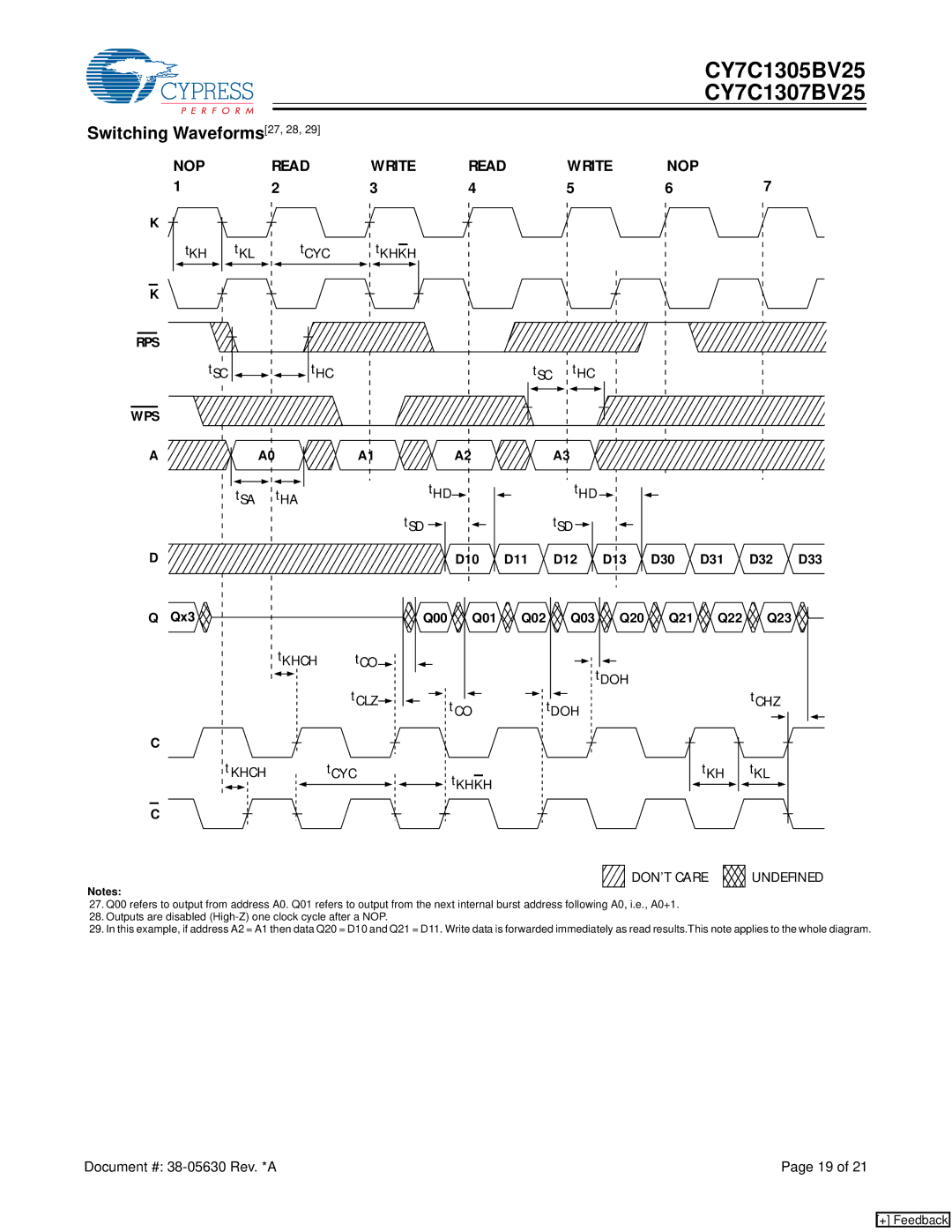

Both the CY7C1305BV25 and CY7C1307BV25 utilize a synchronous interface, allowing for coordinated data transfer with the system clock. This synchronization minimizes latency and improves overall system performance. The use of advanced pipelining techniques enables these devices to process multiple read and write commands concurrently, further boosting throughput.

In terms of reliability and durability, Cypress ensures that these memory chips comply with stringent industry standards. They are designed to withstand a wide temperature range, making them suitable for operation in diverse environments. The robust design includes features that mitigate the risk of data corruption and enhance data integrity, which is a vital consideration in mission-critical applications.

Overall, the CY7C1305BV25 and CY7C1307BV25 represent Cypress Semiconductor's commitment to delivering high-quality, high-performance memory solutions that meet the demanding requirements of modern electronics. Their impressive features, combined with a focus on low power consumption and reliability, make them a preferred choice for engineers and developers aiming to create the next generation of innovative products.