|

|

| CY7C68023/CY7C68024 |

| |

|

|

|

|

|

|

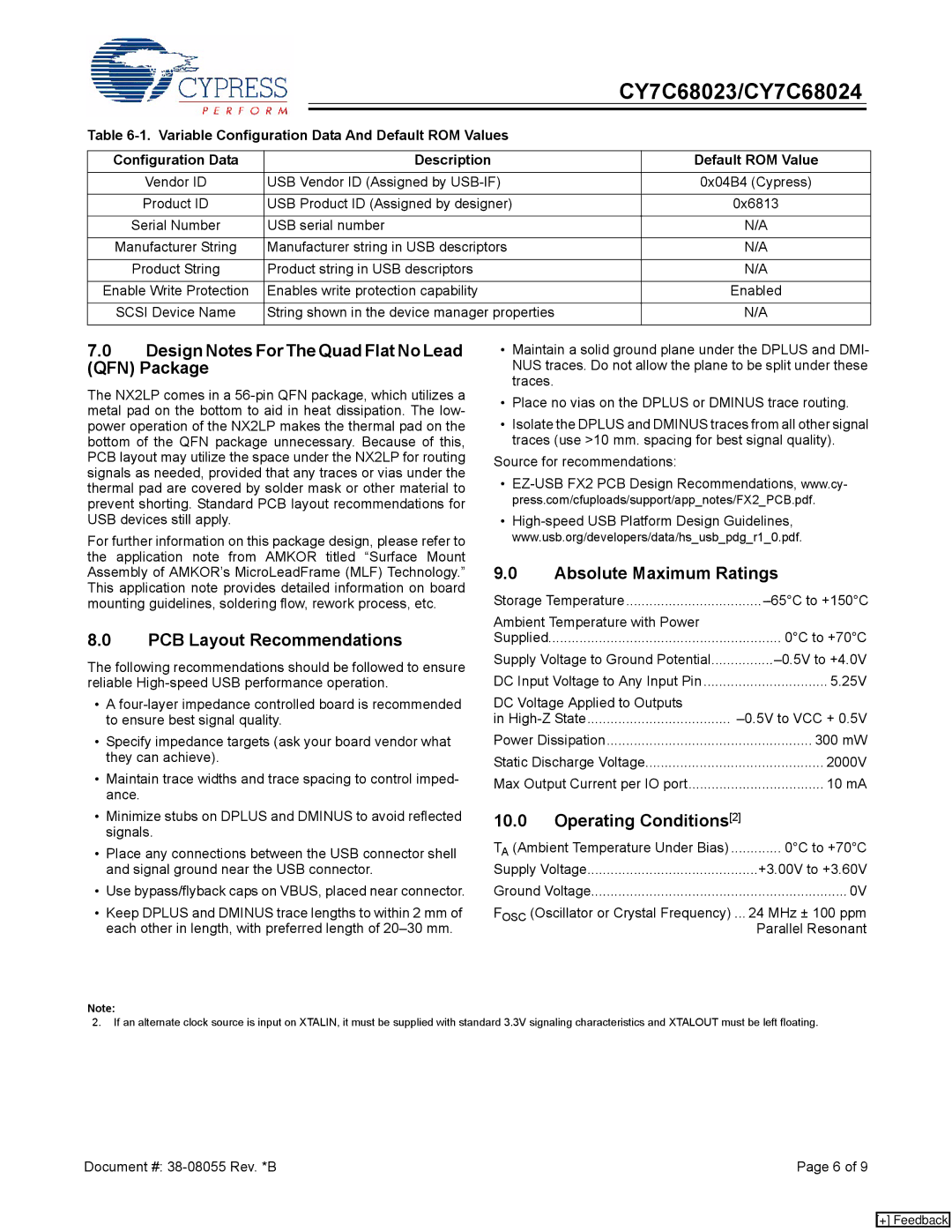

Table |

|

|

| ||

|

|

|

|

|

|

Configuration Data |

| Description |

| Default ROM Value |

|

|

|

|

|

| |

Vendor ID | USB Vendor ID (Assigned by |

| 0x04B4 (Cypress) |

| |

|

|

|

|

| |

Product ID | USB Product ID (Assigned by designer) |

| 0x6813 |

| |

|

|

|

|

| |

Serial Number | USB serial number |

| N/A |

| |

|

|

|

|

| |

Manufacturer String | Manufacturer string in USB descriptors |

| N/A |

| |

|

|

|

|

| |

Product String | Product string in USB descriptors |

| N/A |

| |

|

|

|

|

| |

Enable Write Protection | Enables write protection capability |

| Enabled |

| |

|

|

|

|

| |

SCSI Device Name | String shown in the device manager properties |

| N/A |

| |

|

|

|

|

|

|

7.0Design Notes For The Quad Flat No Lead (QFN) Package

The NX2LP comes in a

For further information on this package design, please refer to the application note from AMKOR titled “Surface Mount Assembly of AMKOR’s MicroLeadFrame (MLF) Technology.” This application note provides detailed information on board mounting guidelines, soldering flow, rework process, etc.

8.0PCB Layout Recommendations

The following recommendations should be followed to ensure reliable

•A

•Specify impedance targets (ask your board vendor what they can achieve).

•Maintain trace widths and trace spacing to control imped- ance.

•Minimize stubs on DPLUS and DMINUS to avoid reflected signals.

•Place any connections between the USB connector shell and signal ground near the USB connector.

•Use bypass/flyback caps on VBUS, placed near connector.

•Keep DPLUS and DMINUS trace lengths to within 2 mm of each other in length, with preferred length of

•Maintain a solid ground plane under the DPLUS and DMI- NUS traces. Do not allow the plane to be split under these traces.

•Place no vias on the DPLUS or DMINUS trace routing.

•Isolate the DPLUS and DMINUS traces from all other signal traces (use >10 mm. spacing for best signal quality).

Source for recommendations:

•

•

9.0Absolute Maximum Ratings

Storage Temperature | |

Ambient Temperature with Power |

|

Supplied | 0°C to +70°C |

Supply Voltage to Ground Potential | |

DC Input Voltage to Any Input Pin | 5.25V |

DC Voltage Applied to Outputs |

|

in | |

Power Dissipation | 300 mW |

Static Discharge Voltage | 2000V |

Max Output Current per IO port | 10 mA |

10.0Operating Conditions[2]

TA (Ambient Temperature Under Bias) | 0°C to +70°C |

Supply Voltage | +3.00V to +3.60V |

Ground Voltage | 0V |

FOSC (Oscillator or Crystal Frequency) ... | 24 MHz ± 100 ppm |

| Parallel Resonant |

Note:

2.If an alternate clock source is input on XTALIN, it must be supplied with standard 3.3V signaling characteristics and XTALOUT must be left floating.

Document #: | Page 6 of 9 |

[+] Feedback