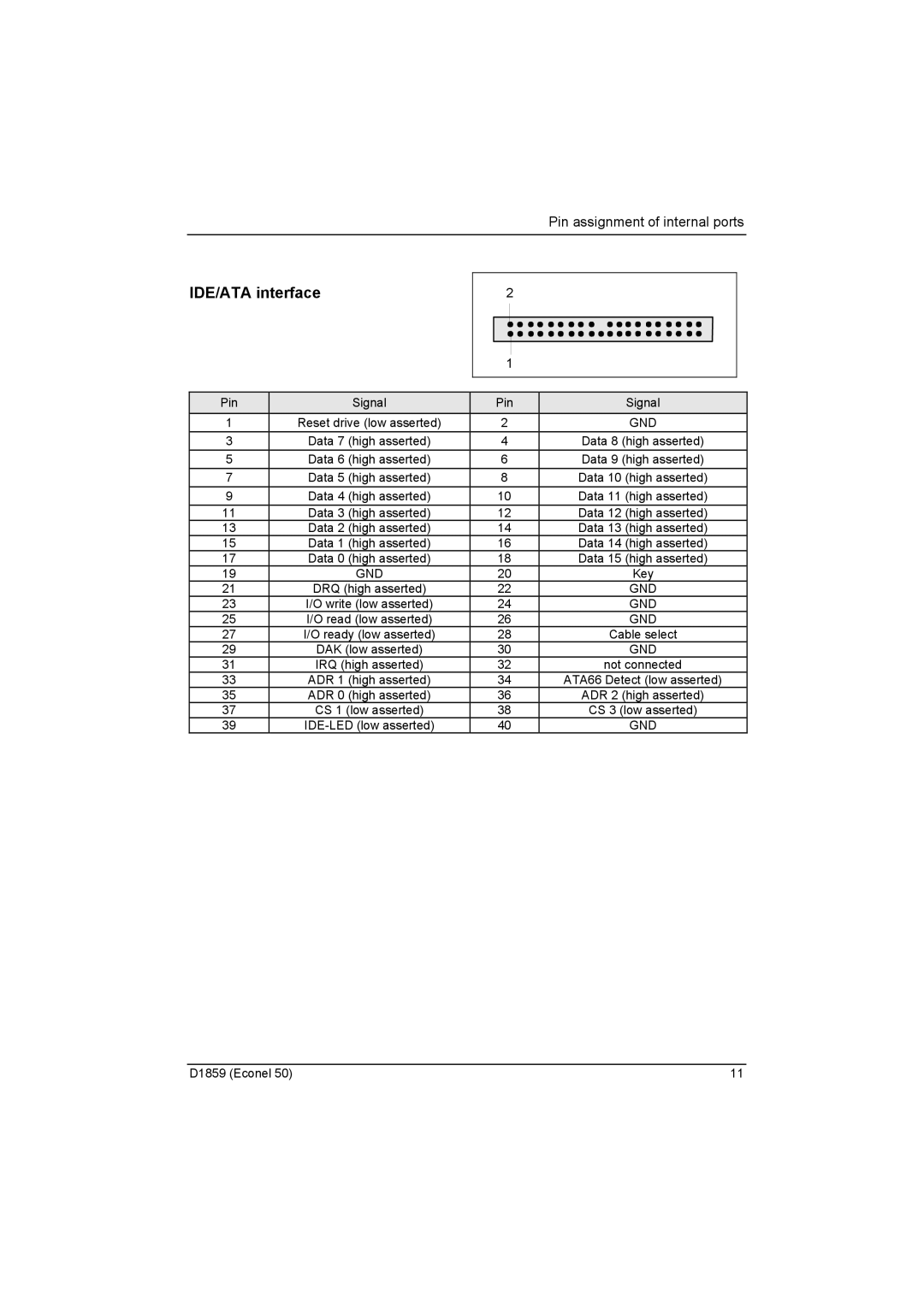

Pin assignment of internal ports

IDE/ATA interface

2 |

1 |

Pin | Signal | Pin | Signal |

1 | Reset drive (low asserted) | 2 | GND |

3 | Data 7 (high asserted) | 4 | Data 8 (high asserted) |

5 | Data 6 (high asserted) | 6 | Data 9 (high asserted) |

7 | Data 5 (high asserted) | 8 | Data 10 (high asserted) |

9 | Data 4 (high asserted) | 10 | Data 11 (high asserted) |

11 | Data 3 (high asserted) | 12 | Data 12 (high asserted) |

13 | Data 2 (high asserted) | 14 | Data 13 (high asserted) |

15 | Data 1 (high asserted) | 16 | Data 14 (high asserted) |

17 | Data 0 (high asserted) | 18 | Data 15 (high asserted) |

19 | GND | 20 | Key |

21 | DRQ (high asserted) | 22 | GND |

23 | I/O write (low asserted) | 24 | GND |

25 | I/O read (low asserted) | 26 | GND |

27 | I/O ready (low asserted) | 28 | Cable select |

29 | DAK (low asserted) | 30 | GND |

31 | IRQ (high asserted) | 32 | not connected |

33 | ADR 1 (high asserted) | 34 | ATA66 Detect (low asserted) |

35 | ADR 0 (high asserted) | 36 | ADR 2 (high asserted) |

37 | CS 1 (low asserted) | 38 | CS 3 (low asserted) |

39 | 40 | GND |

D1859 (Econel 50) | 11 |