| 1 |

|

| 2 |

|

|

| 3 |

| 4 |

|

| |

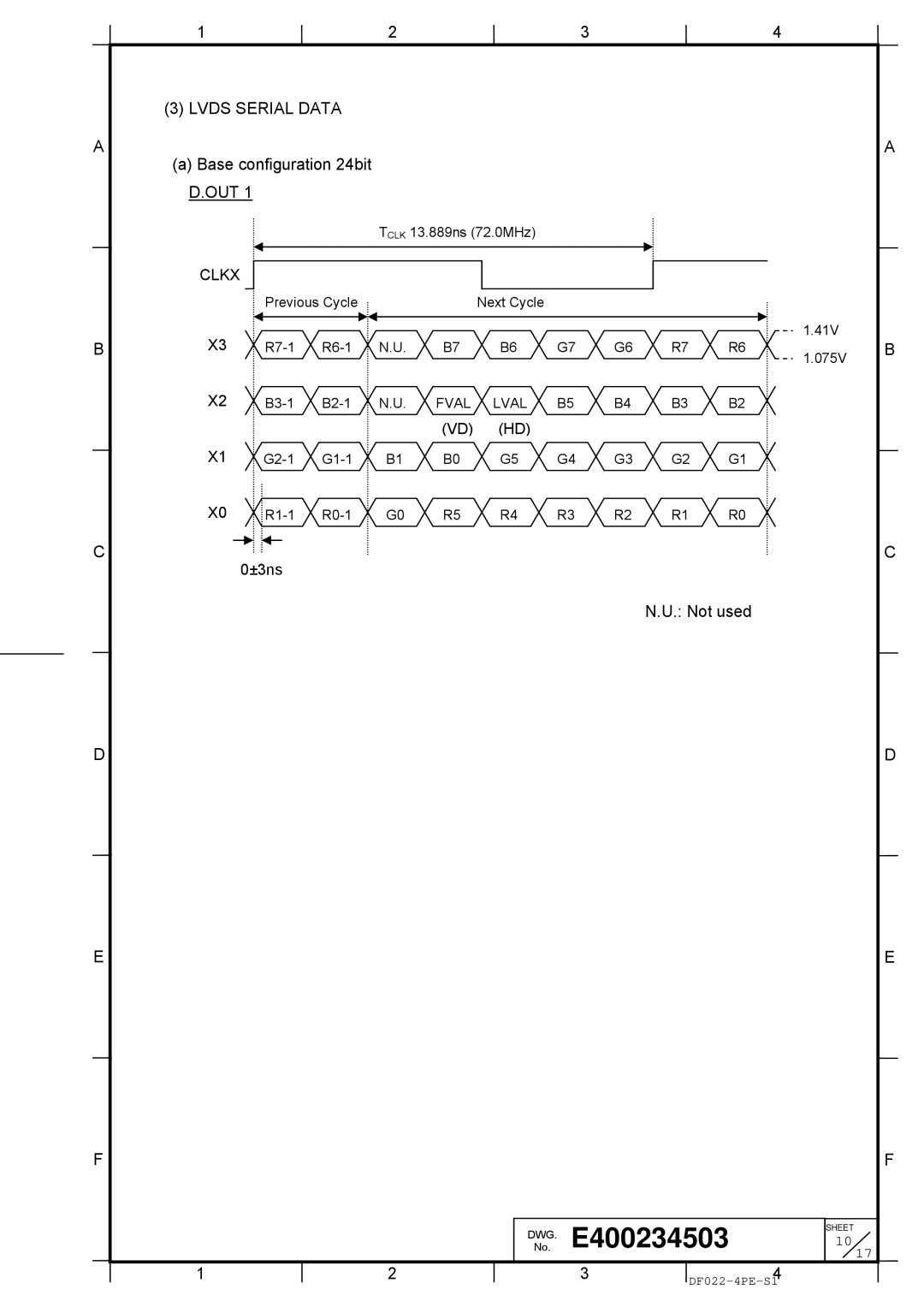

| (3) LVDS SERIAL DATA |

|

|

|

|

|

|

|

|

| |||

A | (a) Base configuration 24bit |

|

|

|

|

|

|

|

| A | |||

|

|

|

|

|

|

|

|

|

| ||||

| D.OUT 1 |

|

|

|

|

|

|

|

|

|

| ||

|

|

|

| TCLK 13.889ns (72.0MHz) |

|

|

|

|

|

| |||

| CLKX |

|

|

|

|

|

|

|

|

|

|

| |

|

| Previous Cycle |

|

| Next Cycle |

|

|

|

|

|

| ||

B | X3 | N.U. | B7 | B6 | G7 | G6 | R7 | R6 | 1.41V | B | |||

1.075V | |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| ||

| X2 | N.U. | FVAL | LVAL | B5 | B4 | B3 | B2 |

|

| |||

|

|

|

|

| (VD) (HD) |

|

|

|

|

|

| ||

| X1 | B1 | B0 | G5 | G4 | G3 | G2 | G1 |

|

| |||

| X0 | G0 | R5 | R4 | R3 | R2 | R1 | R0 |

|

| |||

C |

| 0±3ns |

|

|

|

|

|

|

|

|

| C | |

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| N.U.: Not used |

|

| ||

D |

|

|

|

|

|

|

|

|

|

|

| D | |

E |

|

|

|

|

|

|

|

|

|

|

| E | |

F |

|

|

|

|

|

|

|

|

|

|

| F | |

|

|

|

|

|

| DWG.No. | E400234503 | SHEET |

| ||||

|

|

|

|

|

| 10 | 17 | ||||||

| 1 |

|

| 2 |

|

|

| 3 |

| 4 |

| ||

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

| ||