AMD Smart Fetch Technology

Smart Fetch Technology allows cores to enter a "halt" state during idle processing times, causing them to draw less power. Before entering the halt state, data from the L1 and L2 caches are transferred to the shared L3 cache so that the contents of the idle cores can be retrieved.

Enhanced AMD PowerNow! Technology

Native

Independent Dynamic Core Technology

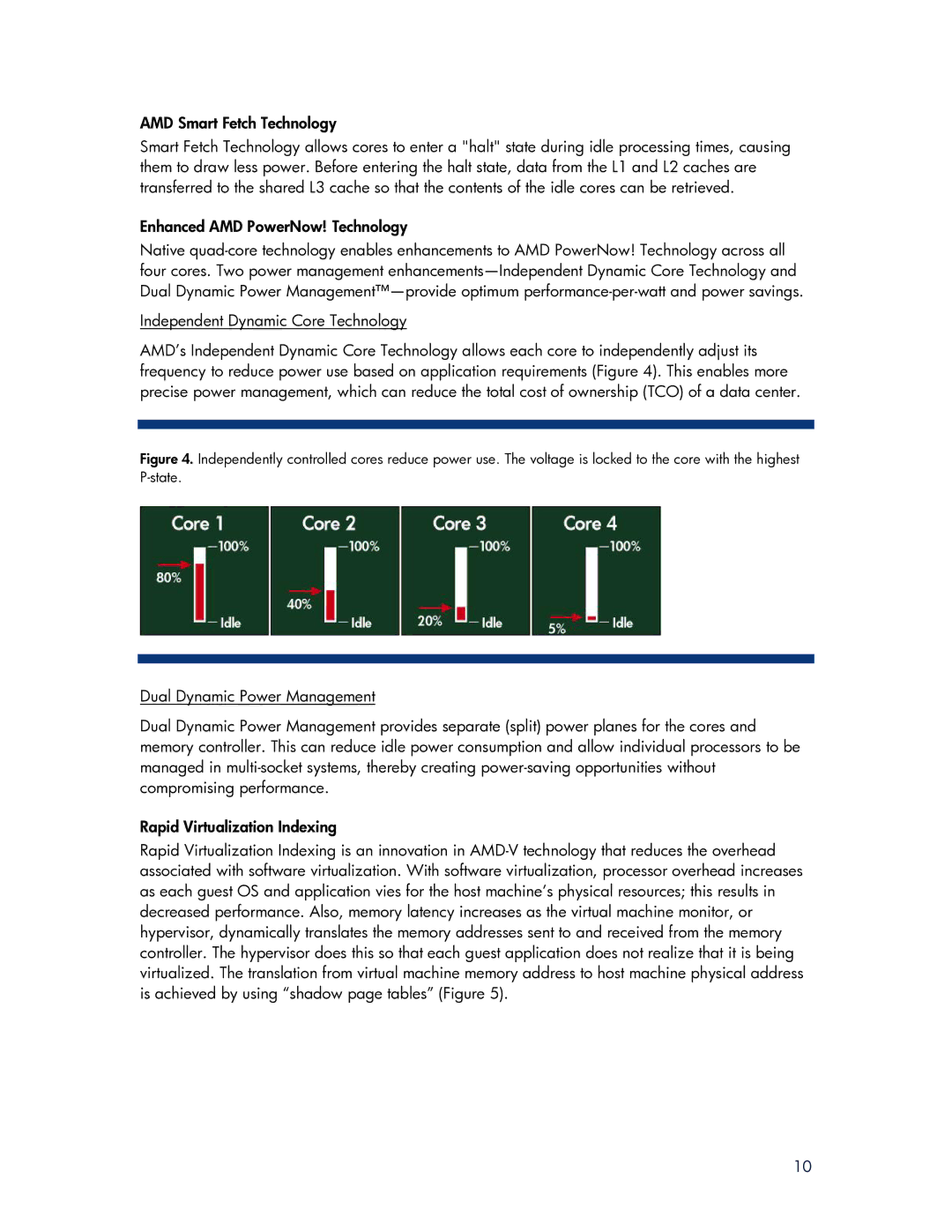

AMD’s Independent Dynamic Core Technology allows each core to independently adjust its frequency to reduce power use based on application requirements (Figure 4). This enables more precise power management, which can reduce the total cost of ownership (TCO) of a data center.

Figure 4. Independently controlled cores reduce power use. The voltage is locked to the core with the highest P-state.

Dual Dynamic Power Management

Dual Dynamic Power Management provides separate (split) power planes for the cores and memory controller. This can reduce idle power consumption and allow individual processors to be managed in

Rapid Virtualization Indexing

Rapid Virtualization Indexing is an innovation in

10