Developer Manual

TVCC

JP3

TVCCP

C10

+

C11

C12

C13

C14

33uF TANT

.1uF

.1uF

.1uF

.1uF

+ BN1 | 1 | TVCC |

|

BANANA JACK |

|

|

|

TVCC |

|

|

|

RED | C7 | C8 | C9 |

| 68 uF | ||

|

| .01uf | .1uf |

BANANA JACK | + BN2 | 1 | VCC |

|

3.3 VOLTS |

|

|

|

|

| RED | C15 | C16 | C17 |

|

| 68 uF | ||

| BN3 |

| .01uf | .1uf |

| - | 1 |

|

|

BANANA JACK |

|

|

| |

|

|

|

|

D1

TVS 5V

D2

TVS 3.3V

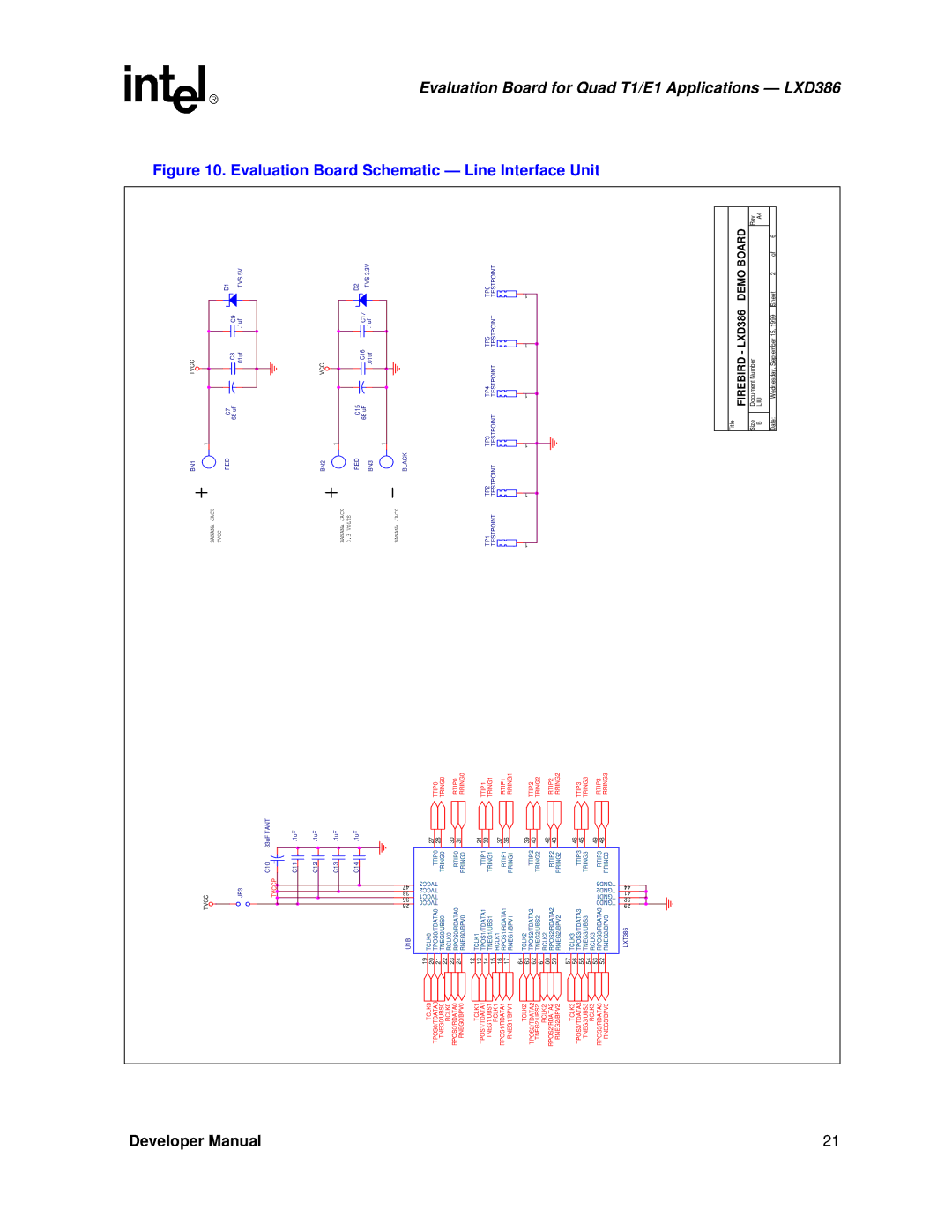

Figure 10. Evaluation BoardSchematic |

|

|

| U1B | 26 35 38 47 |

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

| |

TCLK0 | 19 |

| TCLK0 |

| TVCC0 | TVCC1 | TVCC2 | TVCC3 |

|

|

|

|

20 |

|

|

|

| 27 |

| ||||||

TPOS0/TDATA0 |

| TPOS0/TDATA0 |

| TTIP0 |

| TTIP0 | ||||||

21 |

|

|

| 28 | ||||||||

TNEG0/UBS0 |

| TNEG0/UBS0 |

|

|

|

|

| TRING0 |

| TRING0 | ||

22 |

|

|

|

|

|

|

|

| ||||

RCLK0 |

| RCLK0 |

|

|

|

|

|

|

|

|

| |

23 |

|

|

|

|

|

|

|

| 30 |

| ||

RPOS0/RDATA0 |

| RPOS0/RDATA0 |

|

|

|

| RTIP0 |

| RTIP0 | |||

24 |

|

|

|

|

|

| 31 | |||||

RNEG0/BPV0 |

| RNEG0/BPV0 |

|

|

|

|

| RRING0 |

| RRING0 | ||

12 |

|

|

|

|

|

|

|

| ||||

TCLK1 |

| TCLK1 |

|

|

|

|

|

|

|

|

| |

13 |

|

|

|

|

|

|

|

| 34 |

| ||

TPOS1/TDATA1 |

| TPOS1/TDATA1 |

|

|

|

|

| TTIP1 |

| TTIP1 | ||

14 |

|

|

|

|

|

|

| 33 | ||||

TNEG1/UBS1 |

| TNEG1/UBS1 |

|

|

|

|

| TRING1 |

| TRING1 | ||

15 |

|

|

|

|

|

|

|

| ||||

RCLK1 |

| RCLK1 |

|

|

|

|

|

|

|

|

| |

16 |

|

|

|

|

|

|

|

| 37 |

| ||

RPOS1/RDATA1 |

| RPOS1/RDATA1 |

|

|

|

| RTIP1 |

| RTIP1 | |||

17 |

|

|

|

|

|

| 36 | |||||

RNEG1/BPV1 |

| RNEG1/BPV1 |

|

|

|

|

| RRING1 |

| RRING1 | ||

64 |

|

|

|

|

|

|

|

| ||||

TCLK2 |

| TCLK2 |

|

|

|

|

|

|

|

|

| |

63 |

|

|

|

|

|

| TTIP2 |

| 39 | TTIP2 | ||

TPOS2/TDATA2 |

| TPOS2/TDATA2 |

|

|

|

|

|

| ||||

62 |

|

|

|

|

|

|

| 40 | ||||

TNEG2/UBS2 |

| TNEG2/UBS2 |

|

|

|

|

| TRING2 |

| TRING2 | ||

61 |

|

|

|

|

|

|

|

| ||||

RCLK2 |

| RCLK2 |

|

|

|

|

|

|

|

|

| |

60 |

|

|

|

|

|

|

|

| 42 |

| ||

RPOS2/RDATA2 |

| RPOS2/RDATA2 |

|

|

|

| RTIP2 |

| RTIP2 | |||

59 |

|

|

|

|

|

| 43 | |||||

RNEG2/BPV2 |

| RNEG2/BPV2 |

|

|

|

|

| RRING2 |

| RRING2 | ||

57 |

|

|

|

|

|

|

|

| ||||

TCLK3 |

| TCLK3 |

|

|

|

|

|

|

|

|

| |

56 |

|

|

|

|

|

|

|

| 46 |

| ||

TPOS3/TDATA3 |

| TPOS3/TDATA3 |

|

|

|

|

| TTIP3 |

| TTIP3 | ||

55 |

|

|

|

|

|

|

| 45 | ||||

TNEG3/UBS3 |

| TNEG3/UBS3 |

|

|

|

|

| TRING3 |

| TRING3 | ||

54 |

|

|

|

|

|

|

|

| ||||

RCLK3 |

| RCLK3 |

|

|

|

|

|

|

|

|

| |

53 |

|

| TGND0 | TGND1 | TGND2 | TGND3 |

|

| 49 | RTIP3 | ||

RPOS3/RDATA3 |

|

|

|

|

| |||||||

52 |

| RPOS3/RDATA3 | RTIP3 | 48 | ||||||||

RNEG3/BPV3 |

| RNEG3/BPV3 |

|

|

|

|

| RRING3 |

| RRING3 | ||

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| LXT386 | 29 | 32 | 41 | 44 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BLACK |

TP1 | TP2 | TP3 | TP4 | TP5 | |||||

TESTPOINT | TESTPOINT | TESTPOINT | TESTPOINT | TESTPOINT | |||||

|

|

|

|

|

|

|

|

|

|

1 | 1 | 1 | 1 | 1 |

TP6

TESTPOINT

1

— Line | Evaluation |

Interface Unit | Board for Quad |

| T1/E1Applications |

21

Title | FIREBIRD - LXD386 | DEMO BOARD | ||

| ||||

Size | Document Number |

| Rev | |

B | LIU |

| A4 | |

|

|

|

| |

Date: | Wednesday, September 15, 1999 | Sheet 2 of 6 |

| |

— LXD386 |