Developer Manual

25

|

| 1 | 2 |

|

|

|

|

| Figure |

|

|

|

|

|

|

|

| 14 |

| ||

|

| JP15 |

|

|

|

|

|

|

|

|

TCLK0 |

| 3 | 4 | RCLK0 |

|

|

|

| . |

|

|

|

|

|

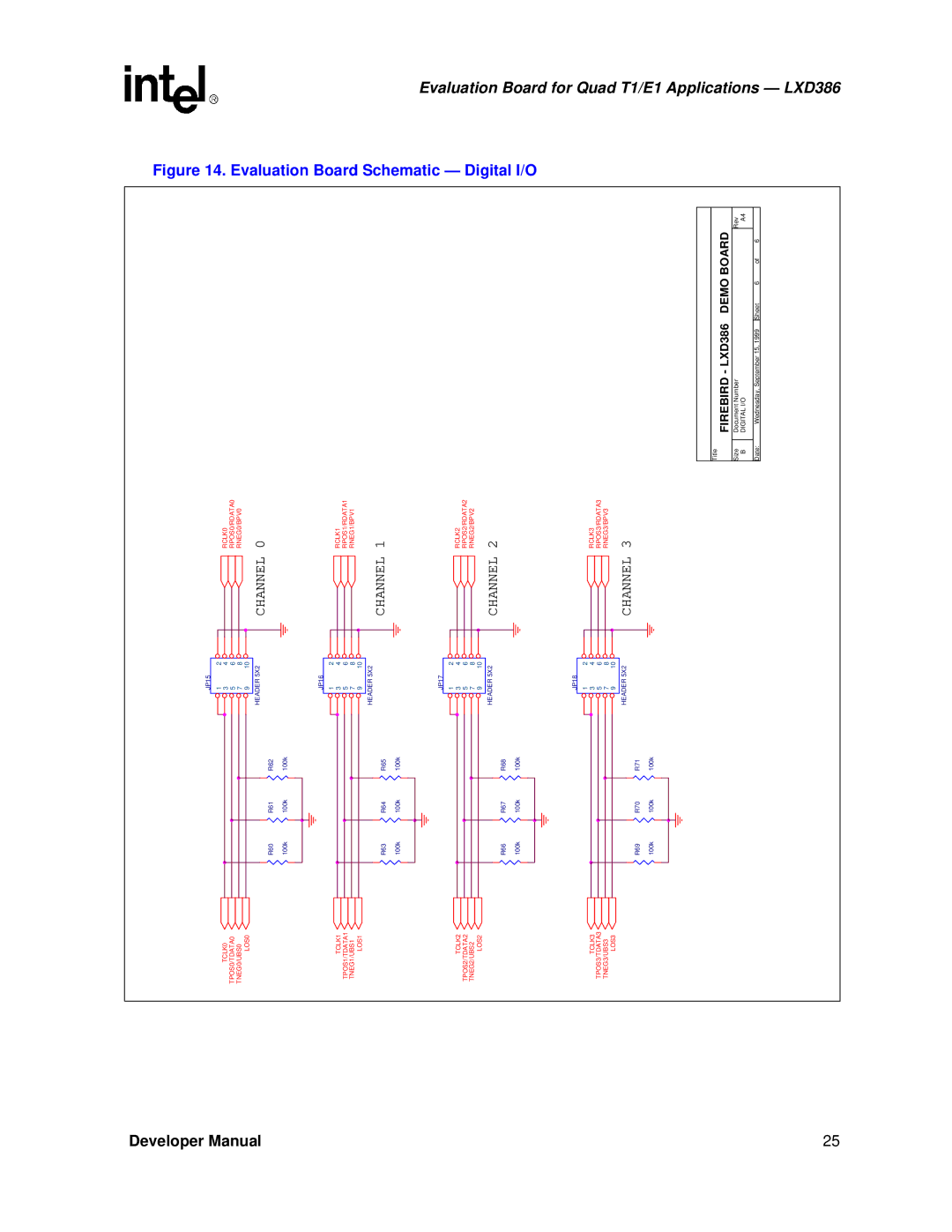

| Evaluation |

| ||||

TPOS0/TDATA0 |

| 5 | 6 | RPOS0/RDATA0 |

|

|

|

|

| |

TNEG0/UBS0 |

| 7 | 8 | RNEG0/BPV0 |

|

|

|

|

| |

LOS0 |

| 9 | 10 |

|

|

|

|

|

|

|

|

| HEADER 5X2 | CHANNEL 0 |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| |

R60 | R61 | R62 |

|

|

|

|

|

|

|

|

100k | 100k | 100k |

|

|

|

|

|

| Board |

|

|

| JP16 |

|

|

|

|

|

|

| |

TCLK1 |

| 1 | 2 | RCLK1 |

|

|

|

|

|

|

| 3 | 4 |

|

|

|

|

|

| ||

TPOS1/TDATA1 |

| 5 | 6 | RPOS1/RDATA1 |

|

|

|

|

|

|

TNEG1/UBS1 |

| 7 | 8 | RNEG1/BPV1 |

|

|

|

|

|

|

LOS1 |

| 9 | 10 |

|

|

|

|

| EvaluationBoard | |

|

| HEADER 5X2 | CHANNEL 1 |

|

|

|

| |||

R63 | R64 | R65 |

|

|

|

|

|

|

| |

100k | 100k | 100k |

|

|

|

|

|

|

|

|

|

| JP17 |

|

|

|

|

|

|

|

|

TCLK2 |

| 1 | 2 | RCLK2 |

|

|

|

|

|

|

| 3 | 4 |

|

|

|

|

|

| ||

TPOS2/TDATA2 |

| 5 | 6 | RPOS2/RDATA2 |

|

|

|

|

|

|

TNEG2/UBS2 |

| 7 | 8 | RNEG2/BPV2 |

|

|

|

|

|

|

LOS2 |

| 9 | 10 |

|

|

|

|

|

|

|

|

| HEADER 5X2 | CHANNEL 2 |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| |

R66 | R67 | R68 |

|

|

|

|

|

|

|

|

100k | 100k | 100k |

|

|

|

|

|

|

|

|

|

| JP18 |

|

|

|

|

|

|

| for |

|

|

|

|

|

|

|

|

| Quad | |

LOS3 |

| 9 | 10 |

|

|

|

|

|

| |

TCLK3 |

| 1 | 2 | RCLK3 |

|

|

|

|

|

|

| 3 | 4 |

|

|

|

|

|

| ||

TPOS3/TDATA3 |

| 5 | 6 | RPOS3/RDATA3 |

|

|

|

|

|

|

TNEG3/UBS3 |

| 7 | 8 | RNEG3/BPV3 |

|

|

|

|

| T1/E1 |

|

| HEADER 5X2 | CHANNEL 3 |

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

| |

R69 | R70 | R71 |

|

|

|

|

|

|

|

|

100k | 100k | 100k |

|

|

|

|

|

|

| Applications |

|

|

|

| Date: | Wednesday, September 15, 1999 | Sheet | 6 | of | 6 | |

|

|

|

| Title | FIREBIRD - LXD386 | DEMO BOARD |

| |||

|

|

|

| Size | Document Number |

|

|

| Rev |

|

|

|

|

| B | DIGITAL I/O |

|

|

| A4 |

|

|

|

|

|

|

|

|

|

|

| — LXD386 |