CV-A11

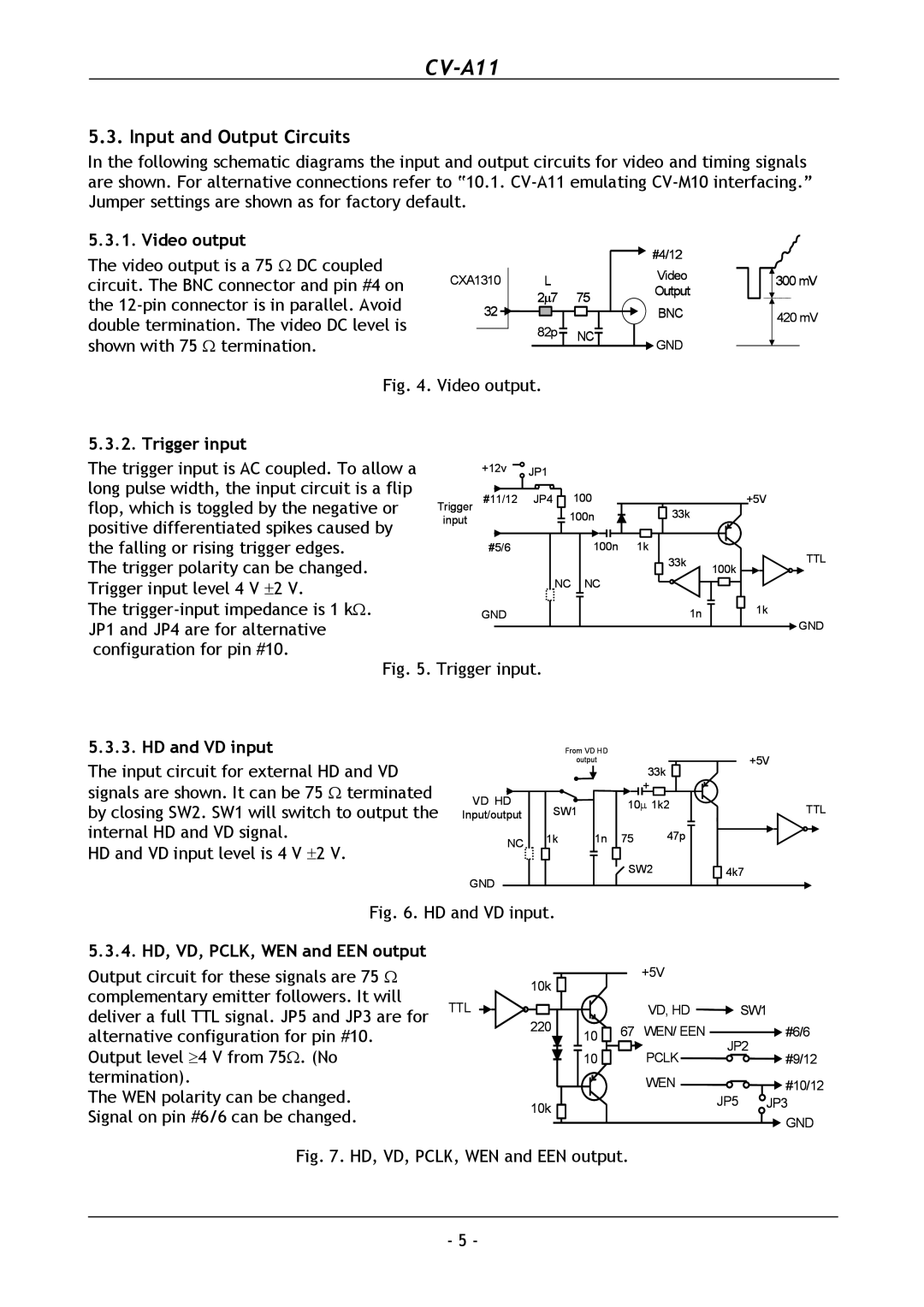

5.3. Input and Output Circuits

In the following schematic diagrams the input and output circuits for video and timing signals are shown. For alternative connections refer to “10.1.

5.3.1. Video output

The video output is a 75 Ω DC coupled circuit. The BNC connector and pin #4 on the

CXA1310

32

L

2∝7 75

82p | NC |

#4/12

Video |

| 300 mV | ||

| ||||

Output |

| |||

|

|

| ||

BNC |

| 420 mV | ||

| ||||

GND |

|

|

|

|

|

|

|

| |

|

|

|

| |

Fig. 4. Video output. |

|

|

| |||

5.3.2. Trigger input |

|

|

|

|

|

|

The trigger input is AC coupled. To allow a |

| +12v | JP1 |

|

|

|

long pulse width, the input circuit is a flip |

| #11/12 | JP4 | 100 |

| +5V |

flop, which is toggled by the negative or | Trigger | 33k | ||||

positive differentiated spikes caused by | input |

| 100n |

| ||

|

|

|

|

|

| |

the falling or rising trigger edges. |

| #5/6 |

| 100n | 1k | TTL |

The trigger polarity can be changed. |

|

|

|

| 33k | |

|

| NC | NC |

| 100k | |

Trigger input level 4 V ±2 V. |

|

|

|

| ||

|

|

|

|

|

| |

The |

| GND |

|

| 1n | 1k |

JP1 and JP4 are for alternative |

|

|

|

|

| GND |

configuration for pin #10. |

|

|

|

|

|

|

Fig. 5. Trigger input. |

|

|

| |||

5.3.3. HD and VD input

From VD HD

output

+5V

The input circuit for external HD and VD signals are shown. It can be 75 Ω terminated by closing SW2. SW1 will switch to output the internal HD and VD signal.

HD and VD input level is 4 V ±2 V.

|

|

|

|

|

|

|

|

VD HD |

|

|

|

|

| SW1 | |

Input/output |

|

|

|

| |||

NC |

|

|

| 1k | |||

GND |

|

|

|

|

|

| |

|

|

|

|

|

| ||

|

|

|

|

| |||

33k ![]()

![]() +

+ ![]()

![]()

10∝ 1k2

1n | 75 | 47p |

![]() SW2

SW2

TTL

![]()

![]() 4k7

4k7

Fig. 6. HD and VD input.

5.3.4. HD, VD, PCLK, WEN and EEN output

Output circuit for these signals are 75 Ω complementary emitter followers. It will deliver a full TTL signal. JP5 and JP3 are for alternative configuration for pin #10. Output level ≥4 V from 75Ω. (No termination).

The WEN polarity can be changed. Signal on pin #6/6 can be changed.

10k |

TTL |

|

220 | 10 |

| |

| 10 |

10k |

|

+5V |

|

|

VD, HD | SW1 | |

67 WEN/ EEN |

| #6/6 |

| ||

JP2

PCLK![]()

![]() #9/12

#9/12

WEN ![]()

![]()

![]() #10/12 JP5 JP3

#10/12 JP5 JP3

![]()

![]() GND

GND

Fig. 7. HD, VD, PCLK, WEN and EEN output.

- 5 -