Hardware Interrupts

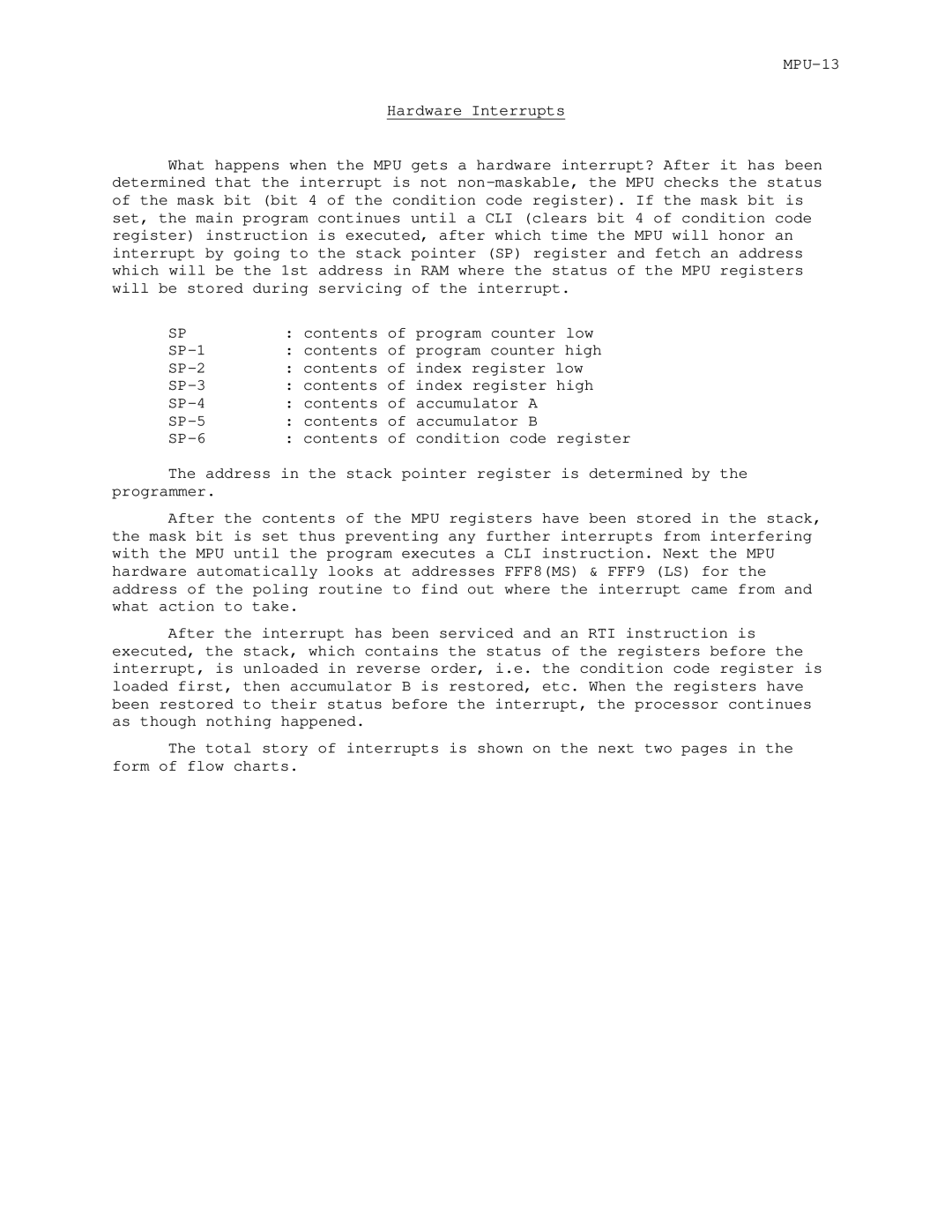

What happens when the MPU gets a hardware interrupt? After it has been determined that the interrupt is not

SP | : contents | of | program counter low |

: contents | of program counter high | ||

: contents | of index register low | ||

: contents | of index register high | ||

: contents of | accumulator A | ||

: contents of | accumulator B | ||

: contents of condition code register | |||

The address in the stack pointer register is determined by the programmer.

After the contents of the MPU registers have been stored in the stack, the mask bit is set thus preventing any further interrupts from interfering with the MPU until the program executes a CLI instruction. Next the MPU hardware automatically looks at addresses FFF8(MS) & FFF9 (LS) for the address of the poling routine to find out where the interrupt came from and what action to take.

After the interrupt has been serviced and an RTI instruction is executed, the stack, which contains the status of the registers before the interrupt, is unloaded in reverse order, i.e. the condition code register is loaded first, then accumulator B is restored, etc. When the registers have been restored to their status before the interrupt, the processor continues as though nothing happened.

The total story of interrupts is shown on the next two pages in the form of flow charts.