MC68030 specifications

The Motorola MC68030 is a highly significant microprocessor that was introduced in 1987 as part of the Motorola 68000 family. This processor was designed to provide advanced performance for a wide range of applications, including workstations, embedded systems, and desktop computers. With its innovative architecture, the MC68030 offered several key features and characteristics that contributed to its popularity.One of the standout features of the MC68030 is its 32-bit architecture, which enhances data handling and processing efficiency. The processor includes a 32-bit data bus and a 32-bit address bus, allowing it to address up to 4 GB of memory directly. This capability was particularly advantageous for applications requiring large data sets and complex calculations.

The MC68030 introduced an improved memory management unit (MMU), which provided virtual memory support. This advanced memory management enables the CPU to use memory more efficiently by allowing it to access more memory than physically available. The MMU also facilitated advanced features such as memory protection and paging, which were essential for multitasking operating systems.

Another significant advancement in the MC68030 was its integrated cache memory. The processor featured an on-chip instruction cache and an optional data cache, which significantly improved performance by reducing memory access latency. The presence of cache memory allowed for faster instruction execution, enabling the MC68030 to achieve higher overall processing speeds compared to its predecessors.

In terms of instruction set architecture, the MC68030 maintained compatibility with the earlier 68000 series while also introducing new instructions and addressing modes. This ensured that software developed for earlier models could still run on the 68030, protecting the investment of companies that had built their systems around the previous models.

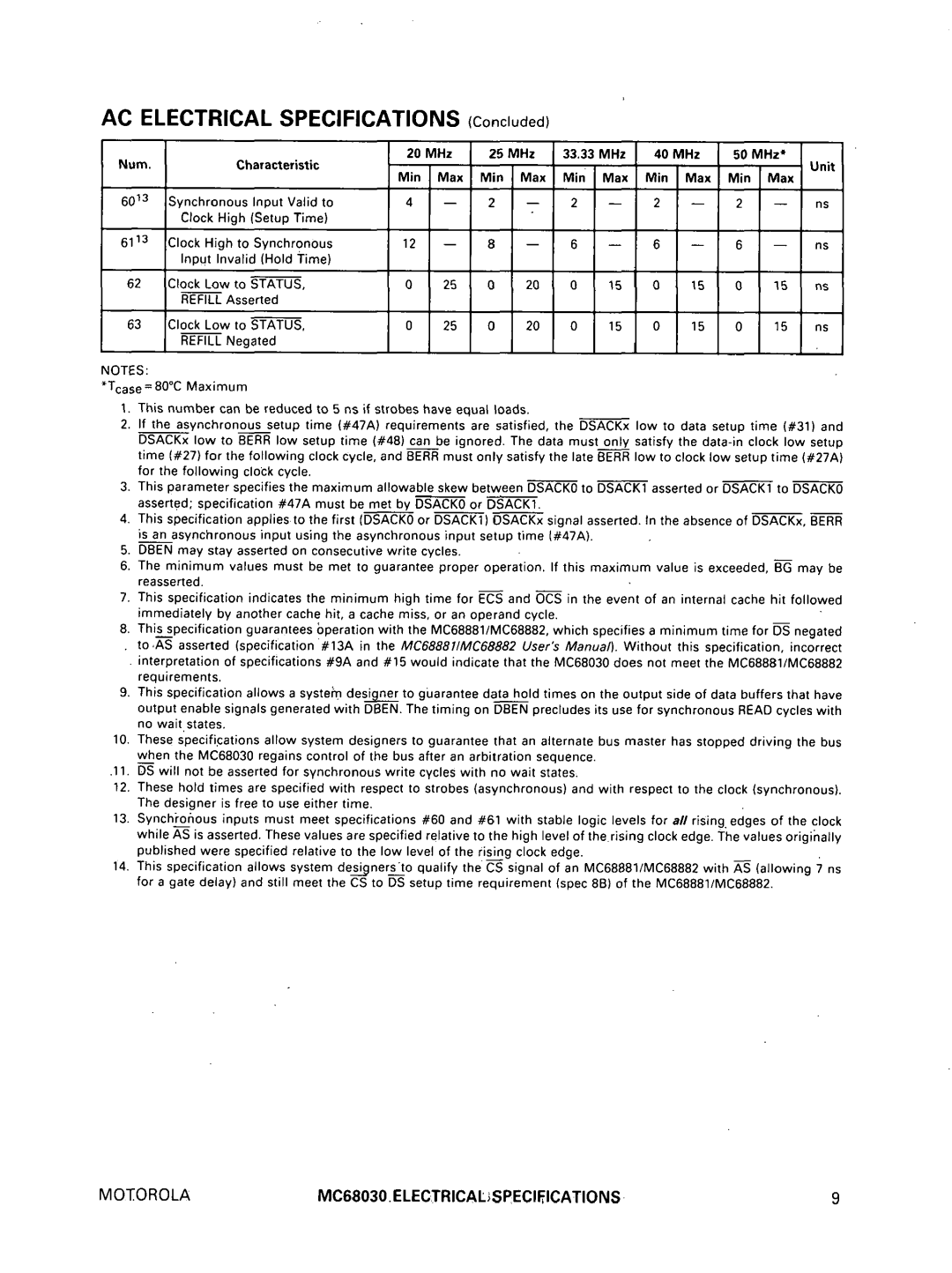

The MC68030 also offered a maximum clock speed of up to 40 MHz, which was quite impressive for its time. This higher clock frequency, coupled with its efficient architectural improvements, allowed the MC68030 to outperform many contemporary processors in both single-task and multi-task scenarios.

In summary, the Motorola MC68030 was a groundbreaking microprocessor that combined 32-bit architecture, advanced memory management, integrated cache, and compatibility with legacy software. Its improved performance and versatility made it a popular choice in various computing environments, from personal computers to sophisticated workstations, leaving a lasting legacy in the evolution of microprocessor technology.