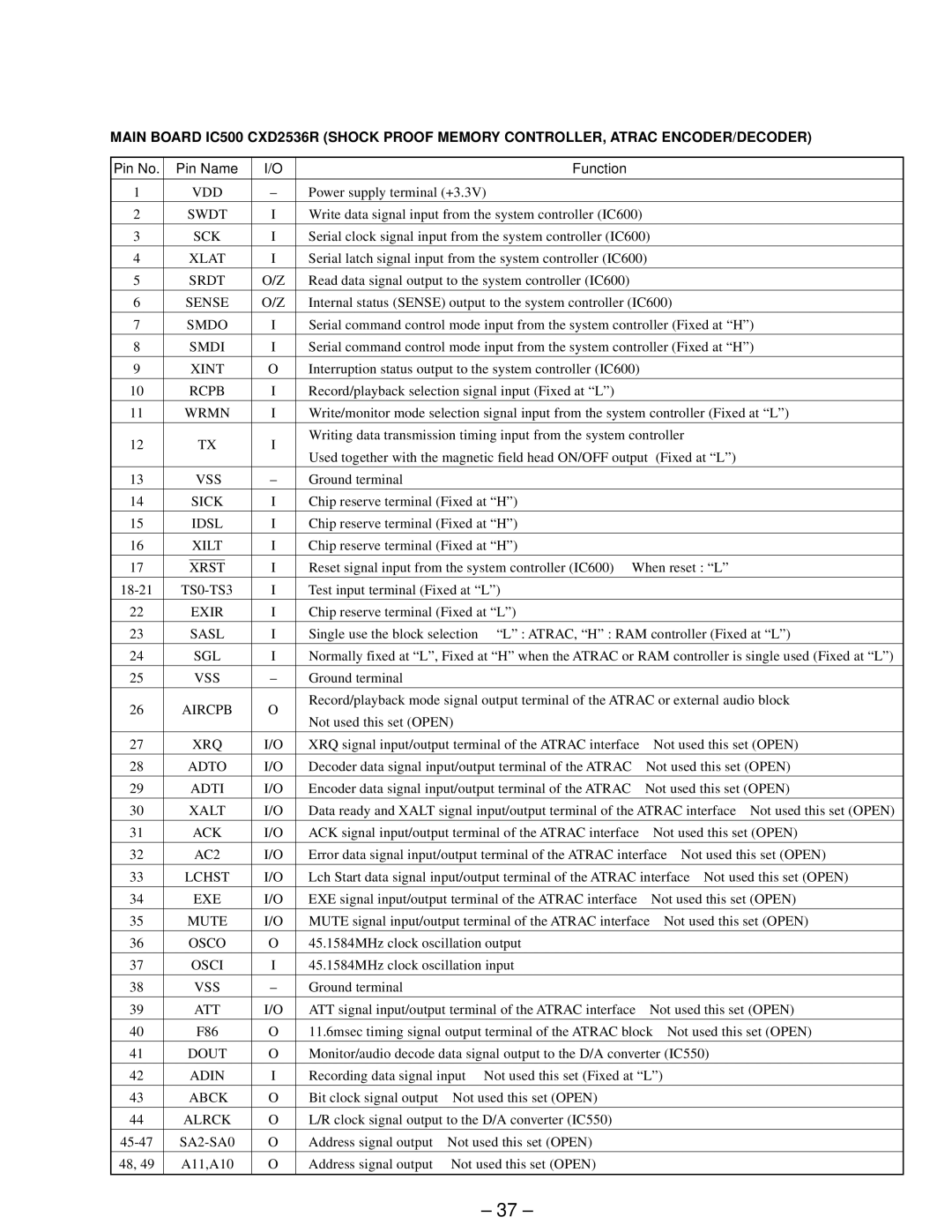

MAIN BOARD IC500 CXD2536R (SHOCK PROOF MEMORY CONTROLLER, ATRAC ENCODER/DECODER)

Pin No. | Pin Name | I/O |

|

| Function |

|

| ||

|

|

|

|

|

|

|

| ||

1 |

| VDD | – | Power supply terminal (+3.3V) |

|

| |||

|

|

|

|

|

|

|

| ||

2 | SWDT | I | Write data signal input from the system controller (IC600) |

|

| ||||

|

|

|

|

|

|

| |||

3 |

| SCK | I | Serial clock signal input from the system controller (IC600) |

| ||||

|

|

|

|

|

|

| |||

4 |

| XLAT | I | Serial latch signal input from the system controller (IC600) |

| ||||

5 |

| SRDT | O/Z | Read data signal output to the system controller (IC600) |

|

| |||

6 | SENSE | O/Z | Internal status (SENSE) output to the system controller (IC600) | ||||||

7 | SMDO | I | Serial command control mode input from the system controller (Fixed at “H”) | ||||||

8 |

| SMDI | I | Serial command control mode input from the system controller (Fixed at “H”) | |||||

|

|

|

|

|

|

|

| ||

9 |

| XINT | O | Interruption status output to the system controller (IC600) |

|

| |||

|

|

|

|

|

|

|

| ||

10 |

| RCPB | I | Record/playback selection signal input (Fixed at “L”) |

|

| |||

|

|

|

|

|

| ||||

11 | WRMN | I | Write/monitor mode selection signal input from the system controller (Fixed at “L”) | ||||||

|

|

|

|

|

| ||||

12 |

| TX | I | Writing data transmission timing input from the system controller | |||||

| Used together with the magnetic field head ON/OFF output | (Fixed at “L”) | |||||||

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

13 |

| VSS | – | Ground terminal |

|

|

|

| |

|

|

|

|

|

|

|

| ||

14 |

| SICK | I | Chip reserve terminal (Fixed at “H”) |

|

| |||

|

|

|

|

|

|

|

| ||

15 |

| IDSL | I | Chip reserve terminal (Fixed at “H”) |

|

| |||

|

|

|

|

|

|

|

| ||

16 |

| XILT | I | Chip reserve terminal (Fixed at “H”) |

|

| |||

|

|

|

|

|

| ||||

17 |

|

|

| I | Reset signal input from the system controller (IC600) When reset : “L” | ||||

| XRST | ||||||||

| I | Test input terminal (Fixed at “L”) |

|

| |||||

22 |

| EXIR | I | Chip reserve terminal (Fixed at “L”) |

|

| |||

23 |

| SASL | I | Single use the block selection | “L” : ATRAC, “H” : RAM controller (Fixed at “L”) | ||||

24 |

| SGL | I | Normally fixed at “L”, Fixed at “H” when the ATRAC or RAM controller is single used (Fixed at “L”) | |||||

|

|

|

|

|

|

|

|

|

|

25 |

| VSS | – | Ground terminal |

|

|

|

| |

|

|

|

|

|

| ||||

26 | AIRCPB | O | Record/playback mode signal output terminal of the ATRAC or external audio block | ||||||

Not used this set (OPEN) |

|

|

| ||||||

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

| ||

27 |

| XRQ | I/O | XRQ signal input/output terminal of the ATRAC interface |

| Not used this set (OPEN) | |||

|

|

|

|

|

|

| |||

28 | ADTO | I/O | Decoder data signal input/output terminal of the ATRAC | Not used this set (OPEN) | |||||

|

|

|

|

|

|

| |||

29 |

| ADTI | I/O | Encoder data signal input/output terminal of the ATRAC | Not used this set (OPEN) | ||||

|

|

|

|

|

| ||||

30 | XALT | I/O | Data ready and XALT signal input/output terminal of the ATRAC interface Not used this set (OPEN) | ||||||

|

|

|

|

|

|

|

| ||

31 |

| ACK | I/O | ACK signal input/output terminal of the ATRAC interface |

| Not used this set (OPEN) | |||

|

|

|

|

|

| ||||

32 |

| AC2 | I/O | Error data signal input/output terminal of the ATRAC interface Not used this set (OPEN) | |||||

|

|

|

|

|

| ||||

33 | LCHST | I/O | Lch Start data signal input/output terminal of the ATRAC interface Not used this set (OPEN) | ||||||

|

|

|

|

|

|

| |||

34 |

| EXE | I/O | EXE signal input/output terminal of the ATRAC interface | Not used this set (OPEN) | ||||

|

|

|

|

|

|

| |||

35 | MUTE | I/O | MUTE signal input/output terminal of the ATRAC interface | Not used this set (OPEN) | |||||

36 | OSCO | O | 45.1584MHz clock oscillation output |

|

| ||||

37 |

| OSCI | I | 45.1584MHz clock oscillation input |

|

| |||

38 |

| VSS | – | Ground terminal |

|

|

|

| |

|

|

|

|

|

|

| |||

39 |

| ATT | I/O | ATT signal input/output terminal of the ATRAC interface | Not used this set (OPEN) | ||||

|

|

|

|

|

|

| |||

40 |

| F86 | O | 11.6msec timing signal output terminal of the ATRAC block | Not used this set (OPEN) | ||||

|

|

|

|

|

| ||||

41 | DOUT | O | Monitor/audio decode data signal output to the D/A converter (IC550) | ||||||

|

|

|

|

|

|

| |||

42 |

| ADIN | I | Recording data signal input | Not used this set (Fixed at “L”) | ||||

|

|

|

|

|

|

|

|

| |

43 | ABCK | O | Bit clock signal output | Not used this set (OPEN) |

|

| |||

|

|

|

|

|

|

|

| ||

44 | ALRCK | O | L/R clock signal output to the D/A converter (IC550) |

|

| ||||

|

|

|

|

|

|

|

|

| |

| O | Address signal output | Not used this set (OPEN) |

|

| ||||

|

|

|

|

|

|

|

|

| |

48, 49 | A11,A10 | O | Address signal output | Not used this set (OPEN) |

|

| |||

|

|

|

|

|

|

|

|

|

|

– 37 –