BIOS Setup Utility |

|

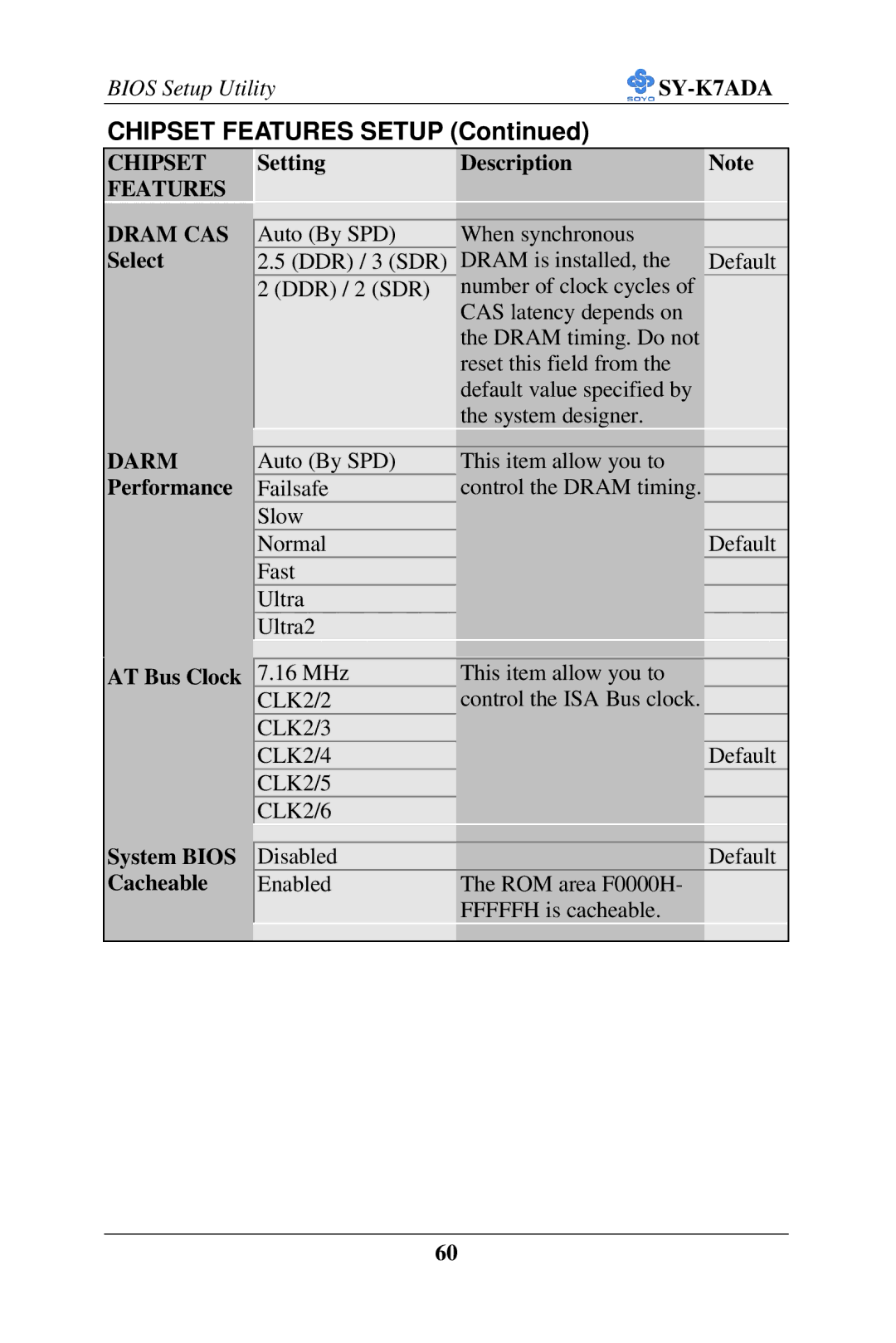

CHIPSET FEATURES SETUP (Continued)

CHIPSET FEATURES

DRAM CAS Select

DARM Performance

| Setting | Description | Note |

|

|

|

|

|

|

|

|

| Auto (By SPD) | When synchronous |

|

| 2.5 (DDR) / 3 (SDR) | DRAM is installed, the | Default |

| 2 (DDR) / 2 (SDR) | number of clock cycles of |

|

|

| CAS latency depends on |

|

|

| the DRAM timing. Do not |

|

|

| reset this field from the |

|

|

| default value specified by |

|

|

| the system designer. |

|

|

|

|

|

| Auto (By SPD) | This item allow you to |

|

| Failsafe | control the DRAM timing. |

|

| Slow |

|

|

| Normal |

| Default |

| Fast |

|

|

Ultra

Ultra2

AT Bus Clock

System BIOS Cacheable

|

|

|

7.16 MHz | This item allow you to |

|

CLK2/2 | control the ISA Bus clock. |

|

CLK2/3 |

|

|

CLK2/4 |

| Default |

CLK2/5 |

|

|

CLK2/6 |

|

|

|

|

|

Disabled |

| Default |

Enabled | The ROM area F0000H- |

|

| FFFFFH is cacheable. |

|

|

|

|

60