12 | The UltraSPARC T2 Processor with CoolThreads Technology | Sun Microsystems, Inc. |

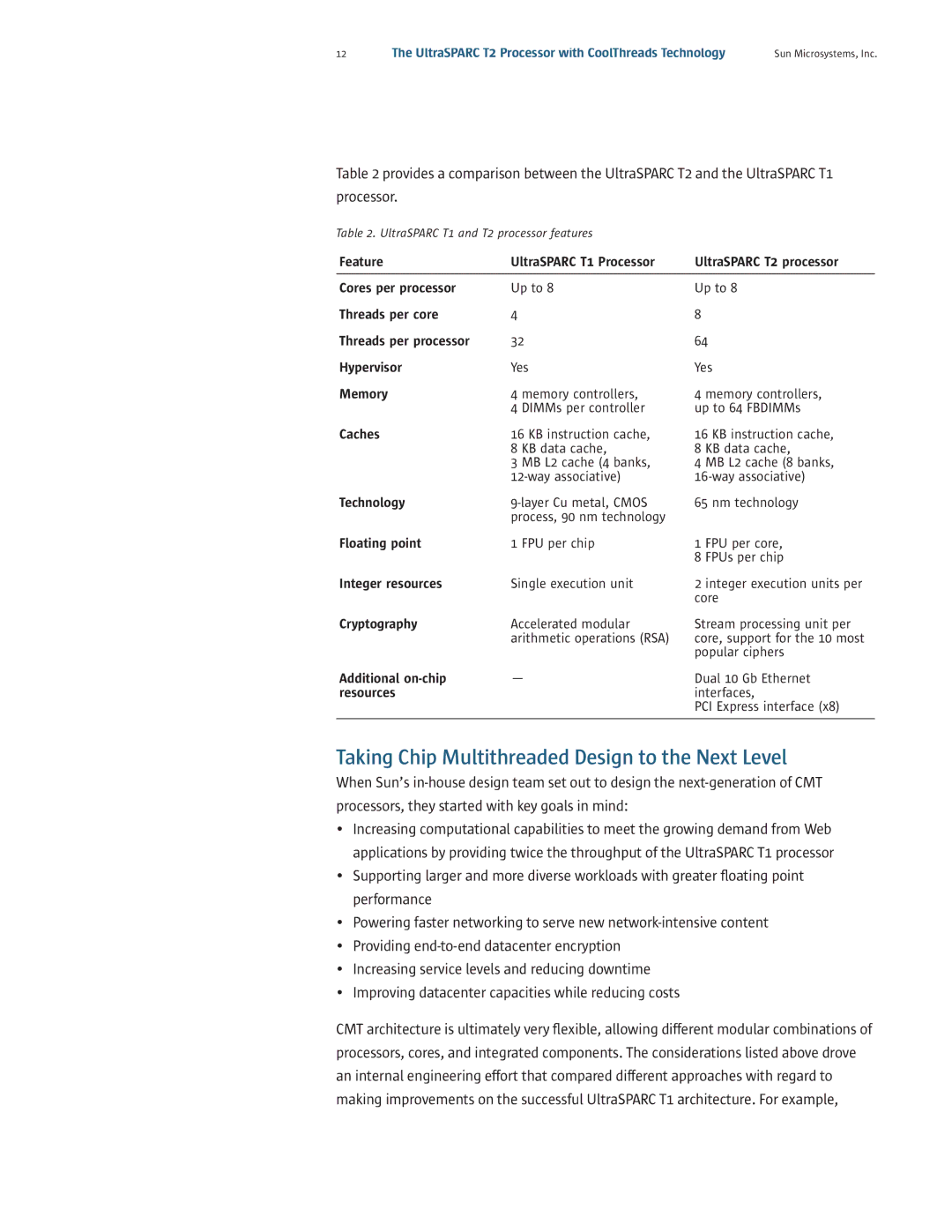

Table 2 provides a comparison between the UltraSPARC T2 and the UltraSPARC T1

processor.

Table 2. UltraSPARC T1 and T2 processor features |

| ||

Feature | UltraSPARC T1 Processor | UltraSPARC T2 processor | |

|

|

| |

Cores per processor | Up to 8 | Up to 8 | |

Threads per core | 4 |

| 8 |

Threads per processor | 32 | 64 | |

Hypervisor | Yes | Yes | |

Memory | 4 memory controllers, | 4 memory controllers, | |

| 4 | DIMMs per controller | up to 64 FBDIMMs |

Caches | 16 KB instruction cache, | 16 KB instruction cache, | |

| 8 | KB data cache, | 8 KB data cache, |

| 3 | MB L2 cache (4 banks, | 4 MB L2 cache (8 banks, |

| |||

Technology | 65 nm technology | ||

| process, 90 nm technology |

| |

Floating point | 1 | FPU per chip | 1 FPU per core, |

|

|

| 8 FPUs per chip |

Integer resources | Single execution unit | 2 integer execution units per | |

|

|

| core |

Cryptography | Accelerated modular | Stream processing unit per | |

| arithmetic operations (RSA) | core, support for the 10 most | |

|

|

| popular ciphers |

Additional | — | Dual 10 Gb Ethernet | |

resources |

|

| interfaces, |

|

|

| PCI Express interface (x8) |

|

|

|

|

Taking Chip Multithreaded Design to the Next Level

When Sun’s

•Increasing computational capabilities to meet the growing demand from Web applications by providing twice the throughput of the UltraSPARC T1 processor

•Supporting larger and more diverse workloads with greater floating point performance

•Powering faster networking to serve new

•Providing

•Increasing service levels and reducing downtime

•Improving datacenter capacities while reducing costs

CMT architecture is ultimately very flexible, allowing different modular combinations of processors, cores, and integrated components. The considerations listed above drove an internal engineering effort that compared different approaches with regard to making improvements on the successful UltraSPARC T1 architecture. For example,