15 | The UltraSPARC T2 Processor with CoolThreads Technology | Sun Microsystems, Inc. |

3DES, AES, RC4,

UltraSPARC T2 Core Architecture and Pipelines

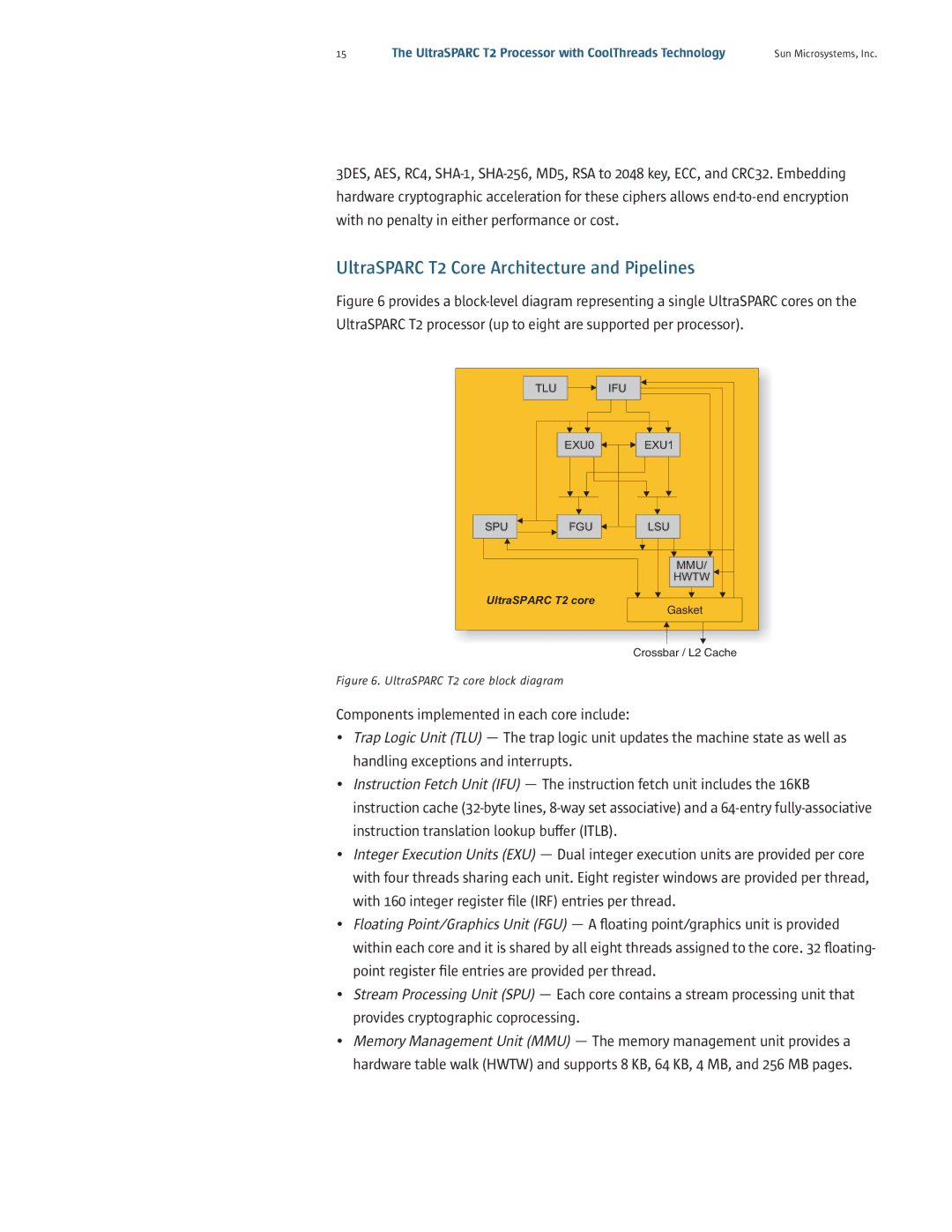

Figure 6 provides a block-level diagram representing a single UltraSPARC cores on the UltraSPARC T2 processor (up to eight are supported per processor).

| TLU | IFU |

| EXU0 | EXU1 |

SPU | FGU | LSU |

|

| MMU/ |

|

| HWTW |

UltraSPARC T2 core | Gasket | |

|

| |

Crossbar / L2 Cache

Figure 6. UltraSPARC T2 core block diagram

Components implemented in each core include:

•Trap Logic Unit (TLU) — The trap logic unit updates the machine state as well as handling exceptions and interrupts.

•Instruction Fetch Unit (IFU) — The instruction fetch unit includes the 16KB instruction cache

•Integer Execution Units (EXU) — Dual integer execution units are provided per core with four threads sharing each unit. Eight register windows are provided per thread, with 160 integer register file (IRF) entries per thread.

•Floating Point/Graphics Unit (FGU) — A floating point/graphics unit is provided within each core and it is shared by all eight threads assigned to the core. 32 floating- point register file entries are provided per thread.

•Stream Processing Unit (SPU) — Each core contains a stream processing unit that provides cryptographic coprocessing.

•Memory Management Unit (MMU) — The memory management unit provides a hardware table walk (HWTW) and supports 8 KB, 64 KB, 4 MB, and 256 MB pages.