Enabling Technology

Next-Generation AMD Opteron Processor Basics

The

•

•Direct Connect Architecture

•Addresses and helps reduce the real challenges and bottlenecks of system architecture

•Memory is directly connected to the CPU, optimizing memory performance

•I/O is directly connected to the CPU, for more balanced throughput and I/O

•CPUS are connected directly to CPUS allowing for more linear symmetrical multiprocessing

•Integrated DDR2 Memory Controller

•A

•AMD HyperTransportTM Technology

•Provides a scalable bandwidth interconnect between processors, I/O subsystems and other chipsets

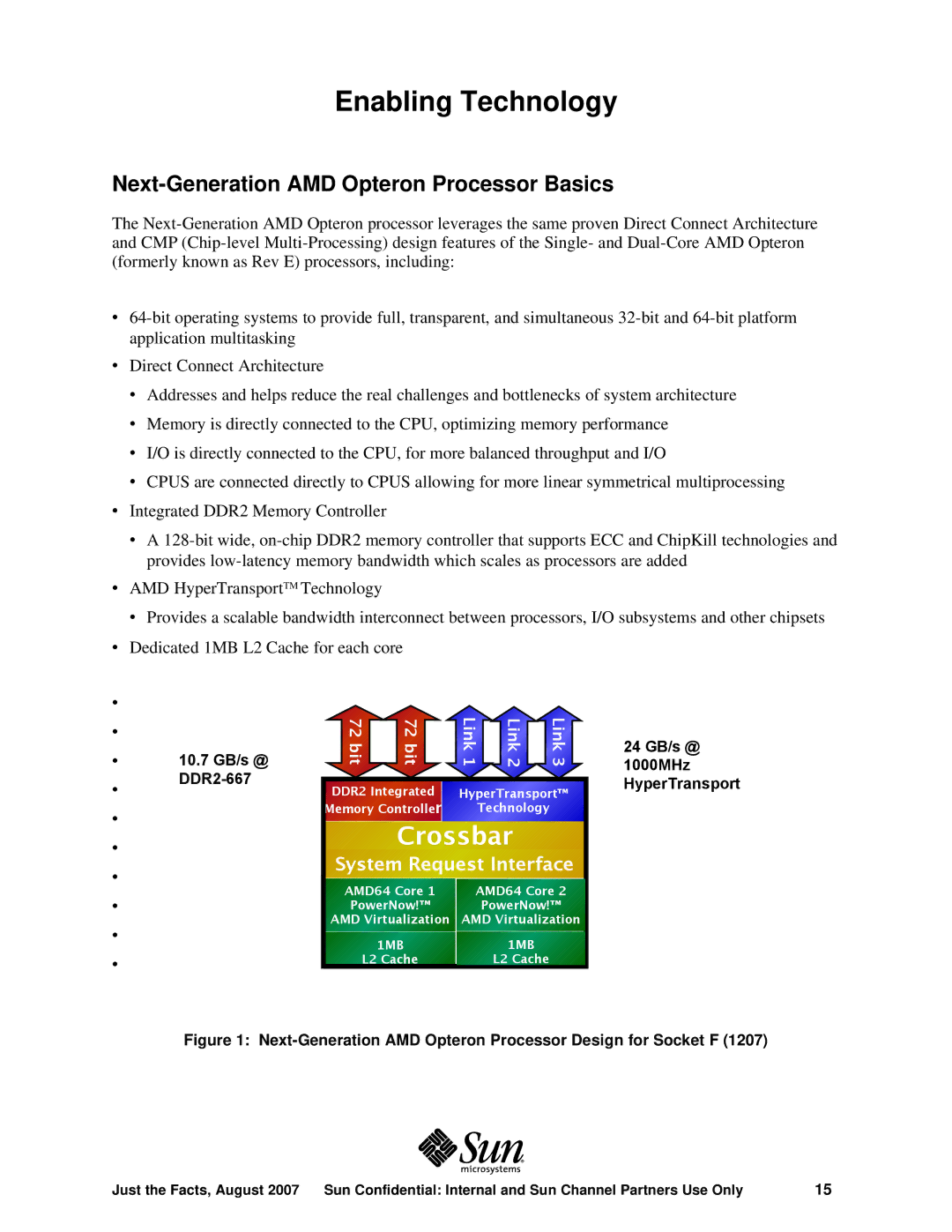

•Dedicated 1MB L2 Cache for each core

•

•

•10.7 GB/s @

•

•

•

•

•

•

•

72bit | 72bit | Link1 | Link2 | Link3 | 24 GB/s @ |

|

|

|

|

| 1000MHz |

DDR2 Integrated | HyperTransport™ | HyperTransport | |||

Memory Controller | Technology |

|

| ||

| Crossbar |

|

| ||

System Request Interface |

| ||||

AMD64 Core 1 | AMD64 Core 2 |

| |||

PowerNow!™ | PowerNow!™ |

| |||

AMD Virtualization | AMD Virtualization |

| |||

| 1MB |

| 1MB |

|

|

L2 Cache |

| L2 Cache |

|

| |

Figure 1: Next-Generation AMD Opteron Processor Design for Socket F (1207)

Just the Facts, August 2007 Sun Confidential: Internal and Sun Channel Partners Use Only | 15 |