HyperTransportTM Technology

The

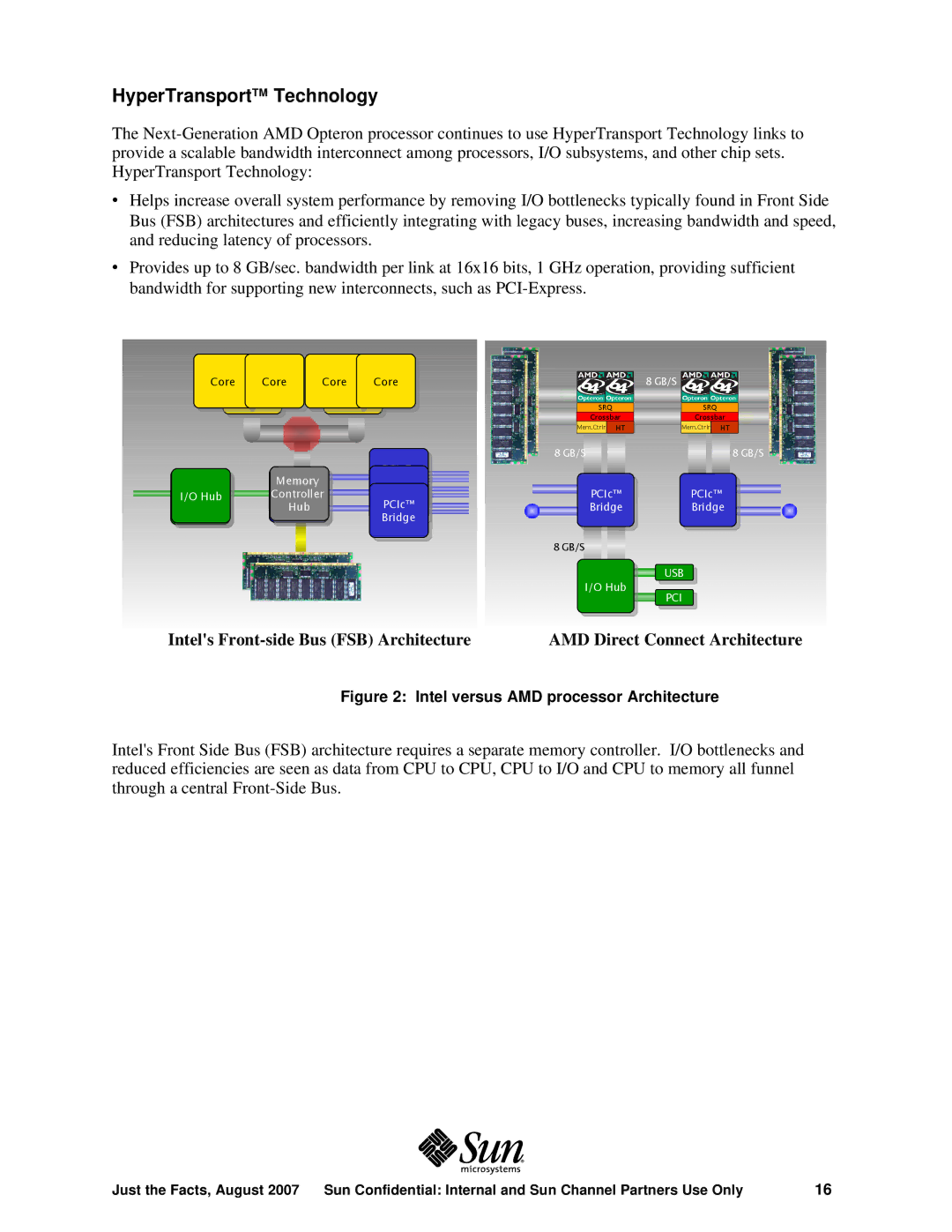

•Helps increase overall system performance by removing I/O bottlenecks typically found in Front Side Bus (FSB) architectures and efficiently integrating with legacy buses, increasing bandwidth and speed, and reducing latency of processors.

•Provides up to 8 GB/sec. bandwidth per link at 16x16 bits, 1 GHz operation, providing sufficient bandwidth for supporting new interconnects, such as

Core | Core | Core | Core |

| 8 GB/S | |

|

|

|

| SRQ | SRQ | |

|

|

|

| Crossbar | Crossbar | |

|

|

|

| Mem.Ctrlr HT | Mem.Ctrlr HT | |

|

|

| 8 GB/S | 8 GB/S | ||

| Memory |

|

|

| ||

|

|

|

| |||

I/O Hub | Controller | PCIc™ | PCIc™ | |||

PCIc™ | ||||||

| Hub |

| Bridge | Bridge | ||

|

|

| Bridge |

|

| |

|

|

|

| 8 GB/S |

| |

|

|

|

| I/O Hub | USB | |

|

|

|

| PCI | ||

|

|

|

|

| ||

Intel's | AMD Direct Connect Architecture | |||||

Figure 2: Intel versus AMD processor Architecture

Intel's Front Side Bus (FSB) architecture requires a separate memory controller. I/O bottlenecks and reduced efficiencies are seen as data from CPU to CPU, CPU to I/O and CPU to memory all funnel through a central

Just the Facts, August 2007 Sun Confidential: Internal and Sun Channel Partners Use Only | 16 |