INTERRUPT CONTROLLER

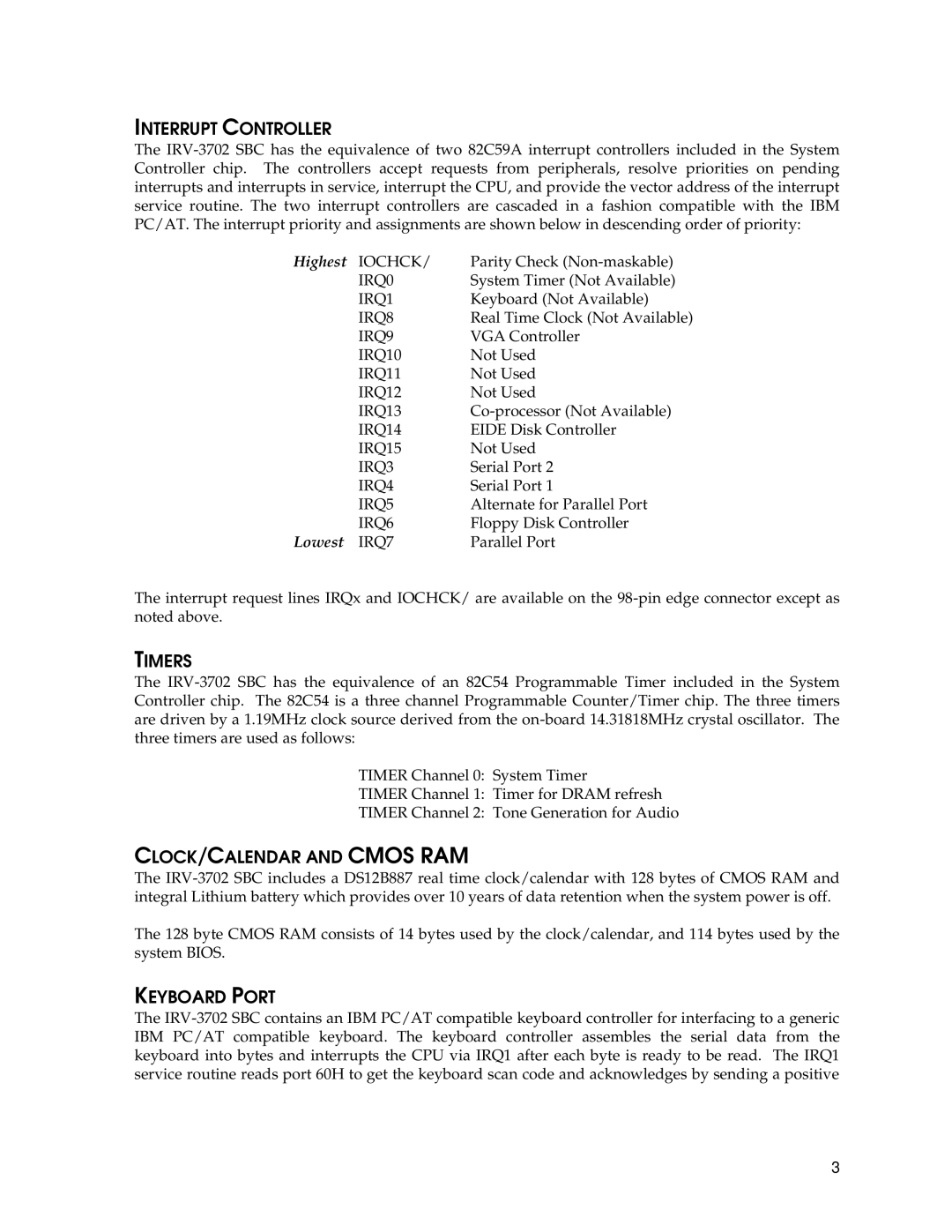

The IRV-3702 SBC has the equivalence of two 82C59A interrupt controllers included in the System Controller chip. The controllers accept requests from peripherals, resolve priorities on pending interrupts and interrupts in service, interrupt the CPU, and provide the vector address of the interrupt service routine. The two interrupt controllers are cascaded in a fashion compatible with the IBM PC/AT. The interrupt priority and assignments are shown below in descending order of priority:

Highest | IOCHCK/ | Parity Check (Non-maskable) |

| IRQ0 | System Timer (Not Available) |

| IRQ1 | Keyboard (Not Available) |

| IRQ8 | Real Time Clock (Not Available) |

| IRQ9 | VGA Controller |

| IRQ10 | Not Used |

| IRQ11 | Not Used |

| IRQ12 | Not Used |

| IRQ13 | Co-processor (Not Available) |

| IRQ14 | EIDE Disk Controller |

| IRQ15 | Not Used |

| IRQ3 | Serial Port 2 |

| IRQ4 | Serial Port 1 |

| IRQ5 | Alternate for Parallel Port |

| IRQ6 | Floppy Disk Controller |

Lowest | IRQ7 | Parallel Port |

The interrupt request lines IRQx and IOCHCK/ are available on the 98-pin edge connector except as noted above.

TIMERS

The IRV-3702 SBC has the equivalence of an 82C54 Programmable Timer included in the System Controller chip. The 82C54 is a three channel Programmable Counter/Timer chip. The three timers are driven by a 1.19MHz clock source derived from the on-board 14.31818MHz crystal oscillator. The three timers are used as follows:

TIMER Channel 0: System Timer

TIMER Channel 1: Timer for DRAM refresh

TIMER Channel 2: Tone Generation for Audio

CLOCK/CALENDAR AND CMOS RAM

The IRV-3702 SBC includes a DS12B887 real time clock/calendar with 128 bytes of CMOS RAM and integral Lithium battery which provides over 10 years of data retention when the system power is off.

The 128 byte CMOS RAM consists of 14 bytes used by the clock/calendar, and 114 bytes used by the system BIOS.

KEYBOARD PORT

The IRV-3702 SBC contains an IBM PC/AT compatible keyboard controller for interfacing to a generic IBM PC/AT compatible keyboard. The keyboard controller assembles the serial data from the keyboard into bytes and interrupts the CPU via IRQ1 after each byte is ready to be read. The IRQ1 service routine reads port 60H to get the keyboard scan code and acknowledges by sending a positive

3