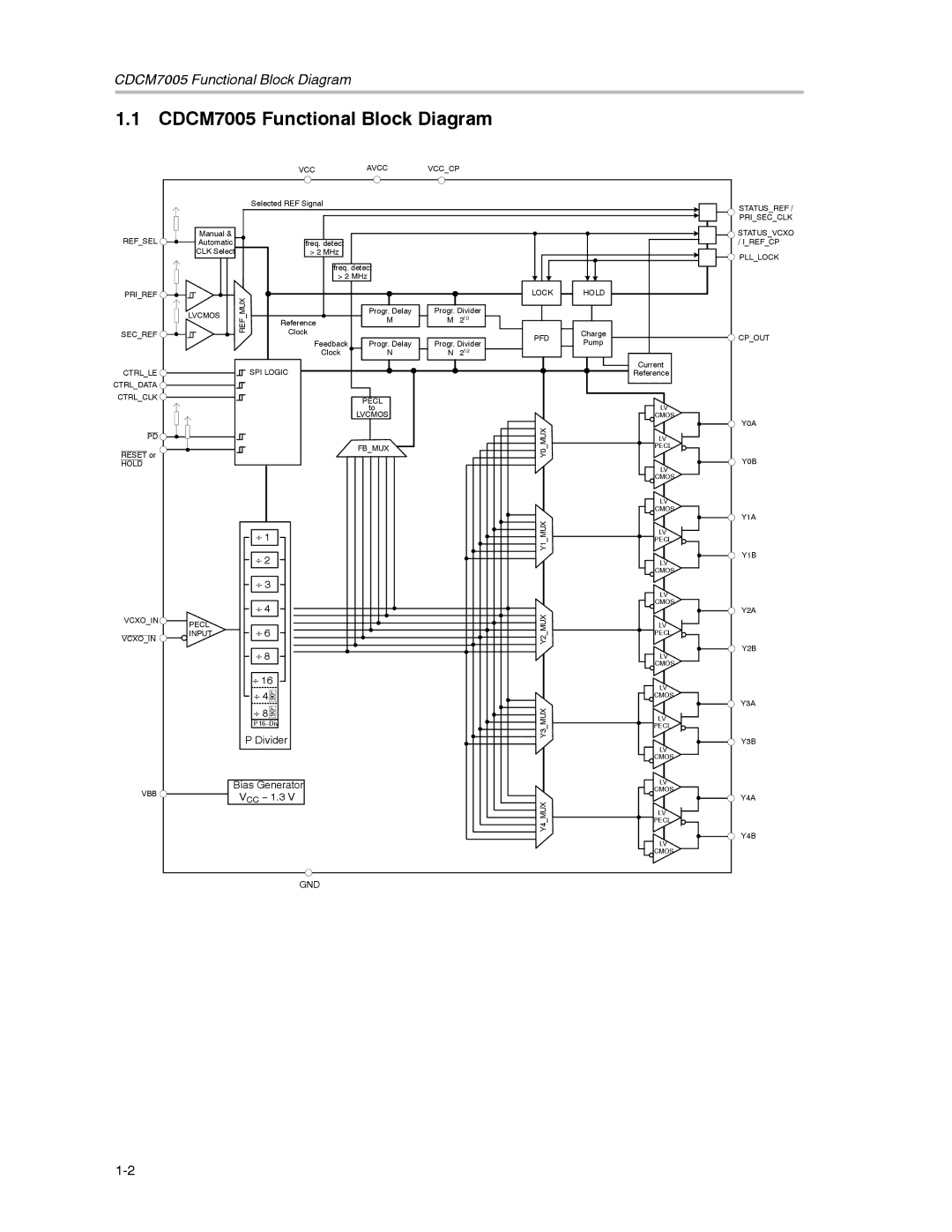

CDCM7005 Functional Block Diagram

1.1 CDCM7005 Functional Block Diagram

|

| VCC | AVCC |

|

| Selected REF Signal |

|

REF_SEL | Manual & |

|

|

Automatic | freq. detect | ||

| CLK Select | > 2 MHz | |

|

|

| freq. detect |

|

|

| > 2 MHz |

PRI_REF |

| MUXREF |

|

| LVCMOS | Progr. Delay | |

| Reference | M | |

|

| ||

|

|

| |

SEC_REF |

| Clock |

|

|

|

| |

| Feedback | Progr. Delay |

| Clock | N |

CTRL_LE | SPI LOGIC |

|

CTRL_DATA |

|

|

CTRL_CLK |

| PECL |

|

| |

|

| to |

|

| LVCMOS |

PD |

|

|

RESET or |

| FB_MUX |

|

| |

HOLD |

|

|

VCC_CP

|

|

|

| STATUS_REF / | |

|

|

|

| PRI_SEC_CLK | |

|

|

|

| STATUS_VCXO | |

|

|

|

| / I_REF_CP | |

|

|

|

| PLL_LOCK | |

|

| LOCK | HOLD |

| |

Progr. Divider |

|

|

| ||

M | 210 |

|

|

| |

|

| PFD | Charge | CP_OUT | |

Progr. Divider | Pump | ||||

|

| ||||

N | 212 |

|

|

| |

|

|

|

| Current | |

|

|

|

| Reference | |

|

|

|

| LV | |

|

|

|

| CMOS | |

|

| Y0 MUX |

| Y0A | |

|

|

| LV | ||

|

|

| PECL | ||

|

|

| Y0B | ||

|

|

|

| ||

|

|

|

| LV | |

|

|

|

| CMOS | |

|

|

|

| LV | |

|

|

|

| CMOS | |

|

|

|

| Y1A | |

VCXO_IN ![]() PECL

PECL

VCXO_IN ![]()

![]() INPUT

INPUT

![]()

![]() ⎟ 1

⎟ 1

![]()

![]() ⎟ 2

⎟ 2

![]()

![]() ⎟ 3

⎟ 3

![]()

![]() ⎟ 4

⎟ 4 ![]()

![]() ⎟ 6

⎟ 6

![]()

![]() ⎟/8

⎟/8

⎟ 16 | |

⎟ 4o90 | |

⎟ 8 | 90o |

| |

P16−Div | |

P Divider

Y1MUX | LV | |

PECL | ||

Y1B | ||

| ||

| LV | |

| CMOS | |

| LV | |

| CMOS | |

Y2 MUX | Y2A | |

LV | ||

PECL | ||

Y2B | ||

| ||

| LV | |

| CMOS | |

| LV | |

| CMOS | |

Y3 MUX | Y3A | |

LV | ||

PECL | ||

Y3B | ||

| ||

| LV | |

| CMOS |

VBB | Bias Generator | |

VCC − 1.3 V | ||

|

| LV | |

| CMOS | |

Y4 MUX | Y4A | |

LV | ||

PECL | ||

Y4B | ||

| ||

| LV | |

| CMOS |

GND