Application Circuit Diagram

5.1 Application Circuit Diagram

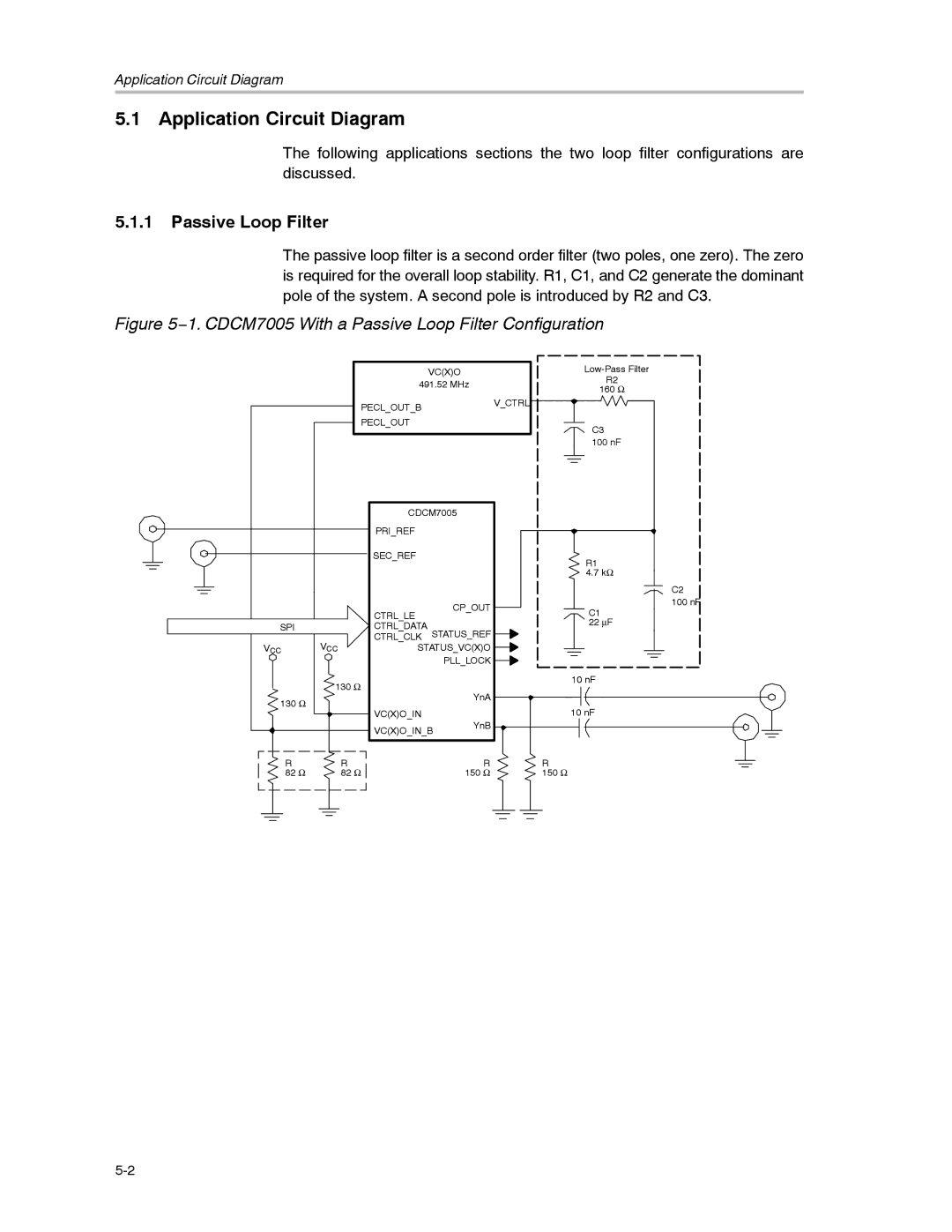

The following applications sections the two loop filter configurations are discussed.

5.1.1Passive Loop Filter

The passive loop filter is a second order filter (two poles, one zero). The zero is required for the overall loop stability. R1, C1, and C2 generate the dominant pole of the system. A second pole is introduced by R2 and C3.

Figure 5−1. CDCM7005 With a Passive Loop Filter Configuration

|

|

|

| VC(X)O |

| ||

|

|

|

|

| R2 | ||

|

|

| 491.52 MHz |

| |||

|

|

|

| 160 Ω | |||

|

|

|

|

|

|

| |

|

|

| PECL_OUT_B |

|

| V_CTRL |

|

|

|

|

|

|

|

| |

|

|

| PECL_OUT |

|

|

| C3 |

|

|

|

|

|

|

| |

|

|

|

|

|

|

| 100 nF |

|

|

| CDCM7005 |

|

| ||

|

|

| PRI_REF |

|

|

|

|

|

|

| SEC_REF |

|

|

| R1 |

|

|

|

|

|

|

| |

|

|

|

|

|

|

| 4.7 kΩ |

|

|

|

|

|

|

| C2 |

|

|

|

|

| CP_OUT |

| 100 nF |

|

|

| CTRL_LE |

|

| C1 | |

|

|

|

|

|

| ||

|

|

|

|

|

| 22 µF | |

SPI |

|

| CTRL_DATA |

|

|

| |

|

| STATUS_REF |

|

| |||

|

| VCC | CTRL_CLK |

|

| ||

VCC |

| STATUS_VC(X)O |

|

| |||

|

|

|

|

| PLL_LOCK |

|

|

|

| 130 Ω |

|

|

| 10 nF | |

|

|

| YnA |

|

| ||

130 Ω |

|

|

|

|

| ||

| VC(X)O_IN |

|

|

| 10 nF | ||

|

|

|

|

|

| ||

|

|

| VC(X)O_IN_B | YnB |

|

| |

|

|

|

|

|

| ||

R | Ω | R | Ω |

| R | R | Ω |

82 | 82 |

| 150 Ω | 150 | |||