www.ti.com

PCB Design and Performance

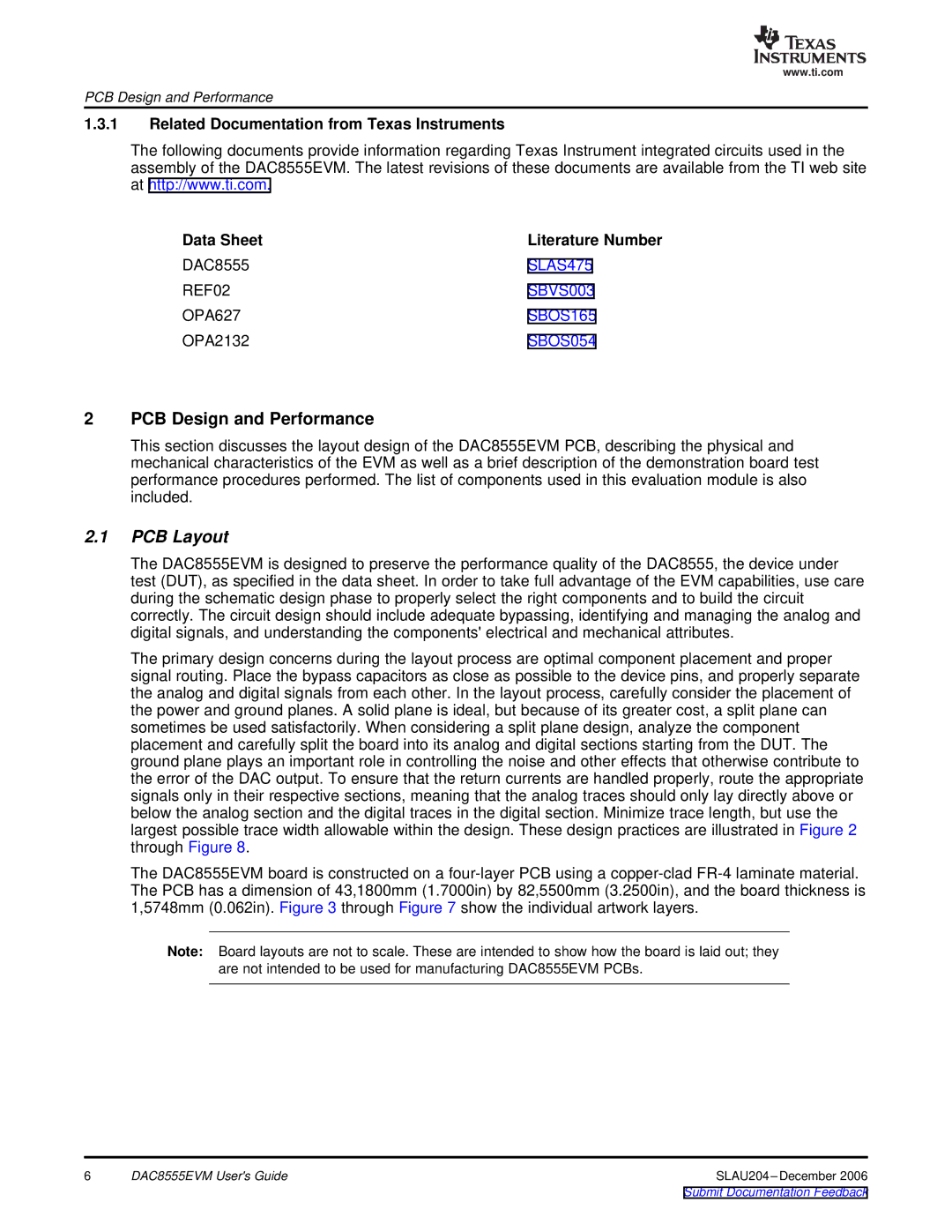

1.3.1Related Documentation from Texas Instruments

The following documents provide information regarding Texas Instrument integrated circuits used in the assembly of the DAC8555EVM. The latest revisions of these documents are available from the TI web site at http://www.ti.com.

Data Sheet | Literature Number |

DAC8555 | SLAS475 |

REF02 | SBVS003 |

OPA627 | SBOS165 |

OPA2132 | SBOS054 |

2PCB Design and Performance

This section discusses the layout design of the DAC8555EVM PCB, describing the physical and mechanical characteristics of the EVM as well as a brief description of the demonstration board test performance procedures performed. The list of components used in this evaluation module is also included.

2.1PCB Layout

The DAC8555EVM is designed to preserve the performance quality of the DAC8555, the device under test (DUT), as specified in the data sheet. In order to take full advantage of the EVM capabilities, use care during the schematic design phase to properly select the right components and to build the circuit correctly. The circuit design should include adequate bypassing, identifying and managing the analog and digital signals, and understanding the components'electrical and mechanical attributes.

The primary design concerns during the layout process are optimal component placement and proper signal routing. Place the bypass capacitors as close as possible to the device pins, and properly separate the analog and digital signals from each other. In the layout process, carefully consider the placement of the power and ground planes. A solid plane is ideal, but because of its greater cost, a split plane can sometimes be used satisfactorily. When considering a split plane design, analyze the component placement and carefully split the board into its analog and digital sections starting from the DUT. The ground plane plays an important role in controlling the noise and other effects that otherwise contribute to the error of the DAC output. To ensure that the return currents are handled properly, route the appropriate signals only in their respective sections, meaning that the analog traces should only lay directly above or below the analog section and the digital traces in the digital section. Minimize trace length, but use the largest possible trace width allowable within the design. These design practices are illustrated in Figure 2 through Figure 8.

The DAC8555EVM board is constructed on a

Note: Board layouts are not to scale. These are intended to show how the board is laid out; they are not intended to be used for manufacturing DAC8555EVM PCBs.

6 | DAC8555EVM User's Guide | SLAU204 |

Submit Documentation Feedback