SPRAA56

In video applications that handle the full resolution of 720x480, each from contains about 675 KB of data. Such applications must constantly move video frames from internal working memory buffers to external frame buffers and back. This often results in several MB of memory transfers through the external bus for each frame. At 30 frames per second, the memory transfer bandwidth requirement can be a significant CPU resource requirement. As resolutions increase to

The architecture of the video software framework often determines the amount of memory bandwidth required. Frameworks that repeatedly move video frames from external memory to internal working buffers and back introduce unnecessary memory bandwidth overhead that may limit the frame rate. Therefore, it is important to understand the memory bus utilization of the whole system and its components.

Data structures for measuring the memory bus utilization of the input, processing, and display tasks are included in the modified example. The actual values logged into the data structures are estimated, based on the defined size of the frames being moved to internal buffers for processing.

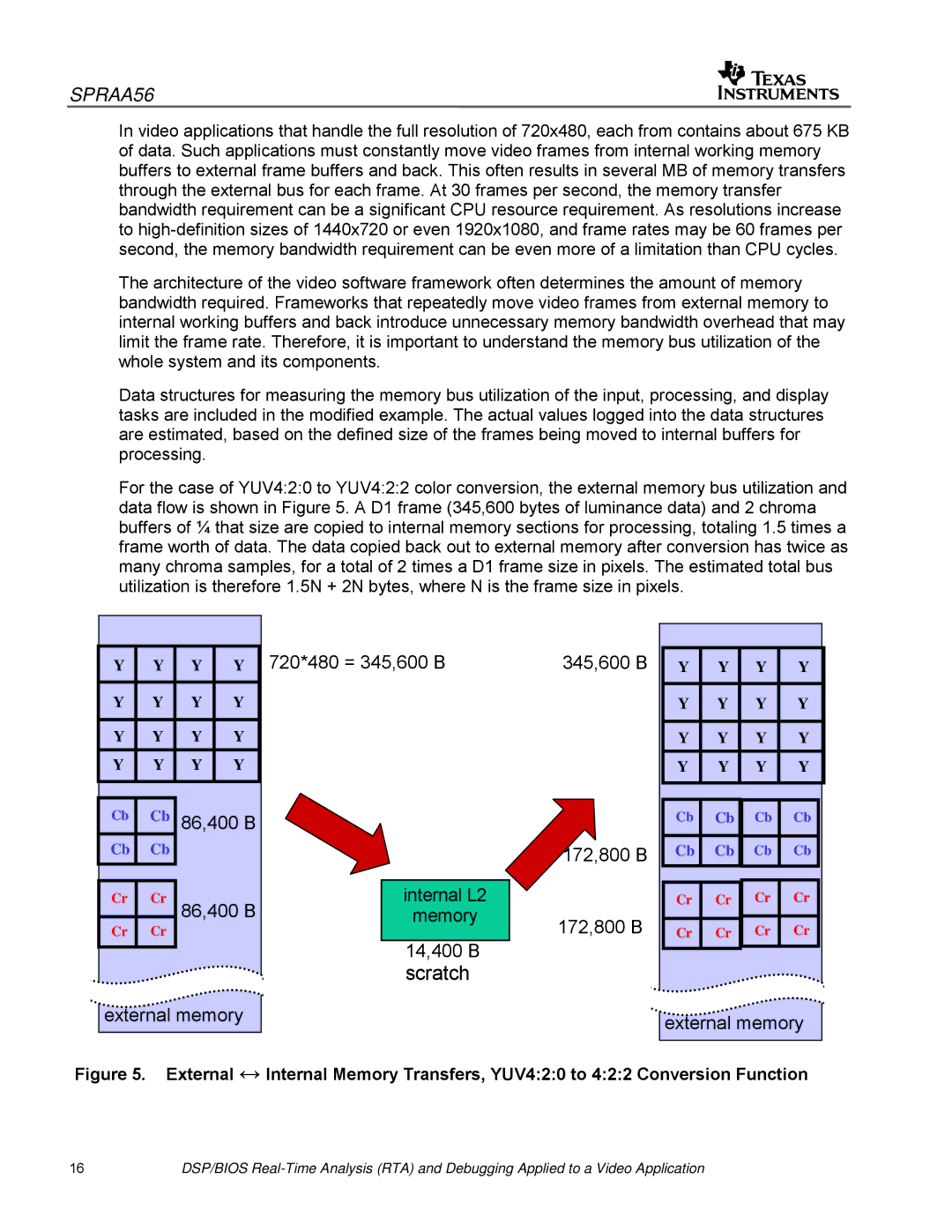

For the case of YUV4:2:0 to YUV4:2:2 color conversion, the external memory bus utilization and data flow is shown in Figure 5. A D1 frame (345,600 bytes of luminance data) and 2 chroma buffers of ¼ that size are copied to internal memory sections for processing, totaling 1.5 times a frame worth of data. The data copied back out to external memory after conversion has twice as many chroma samples, for a total of 2 times a D1 frame size in pixels. The estimated total bus utilization is therefore 1.5N + 2N bytes, where N is the frame size in pixels.

|

|

|

| 720*480 = 345,600 B | ||

Y | Y | Y | Y | |||

|

|

|

|

|

|

|

Y | Y | Y | Y |

|

|

|

|

|

|

|

|

|

|

Y | Y | Y | Y |

|

|

|

Y | Y | Y | Y |

|

|

|

|

|

|

|

|

|

|

|

| 86,400 B |

|

|

| |

Cb | Cb |

|

|

| ||

|

|

|

|

|

| |

|

|

|

|

|

|

|

Cb | Cb |

|

|

|

|

|

|

|

|

|

|

|

|

Cr | Cr | 86,400 B |

|

| internal L2 | |

|

|

|

| memory | ||

Cr | Cr |

|

| |||

|

|

|

|

| ||

|

|

|

|

|

| 14,400 B |

external memory |

|

| scratch | |||

|

|

| ||||

|

|

| ||||

|

|

|

|

|

|

|

345,600 B

172,800 B

172,800 B

Y | Y | Y | Y | |

|

|

|

|

|

Y | Y | Y | Y | |

|

|

|

|

|

Y | Y | Y | Y | |

Y | Y | Y | Y | |

|

|

|

|

|

|

|

|

|

|

Cb | Cb | Cb | Cb |

|

|

|

|

|

|

Cb | Cb | Cb | Cb |

|

|

|

|

|

|

|

|

|

|

|

Cr | Cr | Cr | Cr |

|

|

|

|

|

|

Cr | Cr | Cr | Cr |

|

|

|

|

|

|

![]() external memory

external memory

Figure 5. External ↔ Internal Memory Transfers, YUV4:2:0 to 4:2:2 Conversion Function

16DSP/BIOS