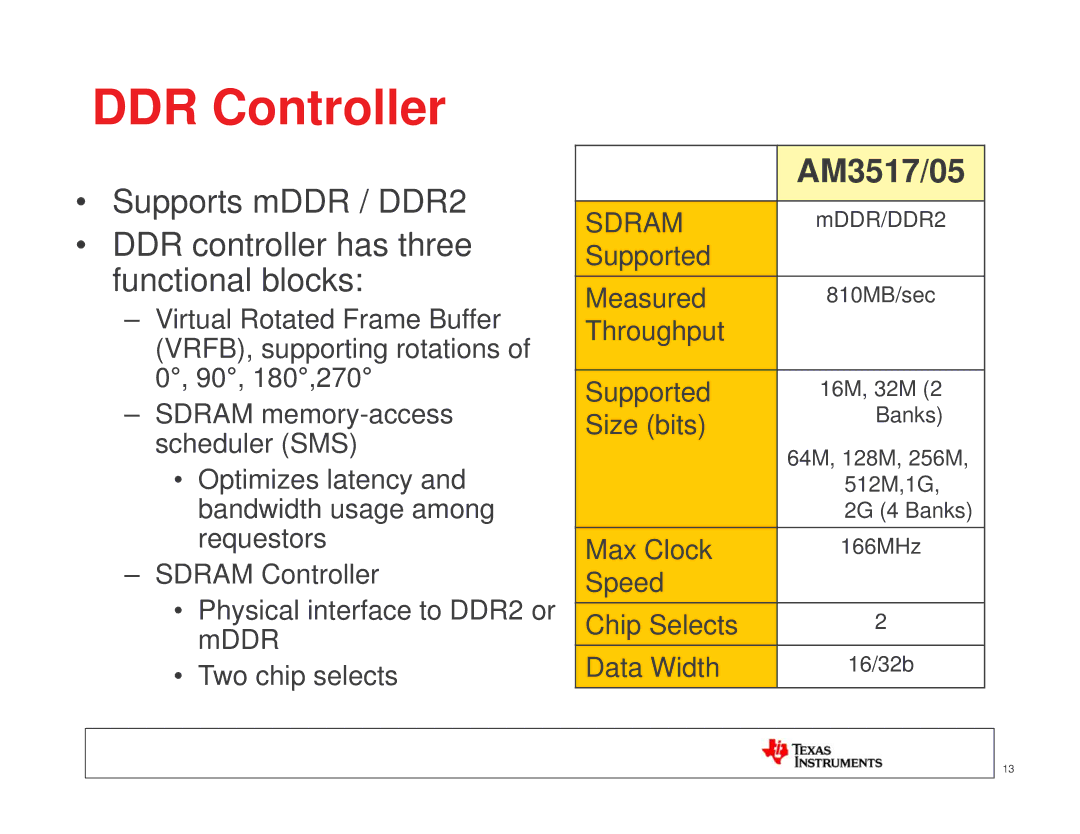

DDR Controller

•Supports mDDR / DDR2

•DDR controller has three functional blocks:

–Virtual Rotated Frame Buffer (VRFB), supporting rotations of 0![]() , 90

, 90![]() , 180

, 180![]() ,270

,270![]()

–SDRAM

•Optimizes latency and bandwidth usage among requestors

–SDRAM Controller

•Physical interface to DDR2 or mDDR

•Two chip selects

| AM3517/05 |

|

|

SDRAM | mDDR/DDR2 |

Supported |

|

|

|

Measured | 810MB/sec |

Throughput |

|

|

|

Supported | 16M, 32M (2 |

Size (bits) | Banks) |

| 64M, 128M, 256M, |

| 512M,1G, |

| 2G (4 Banks) |

Max Clock | 166MHz |

Speed |

|

Chip Selects | 2 |

Data Width | 16/32b |

|

|

13