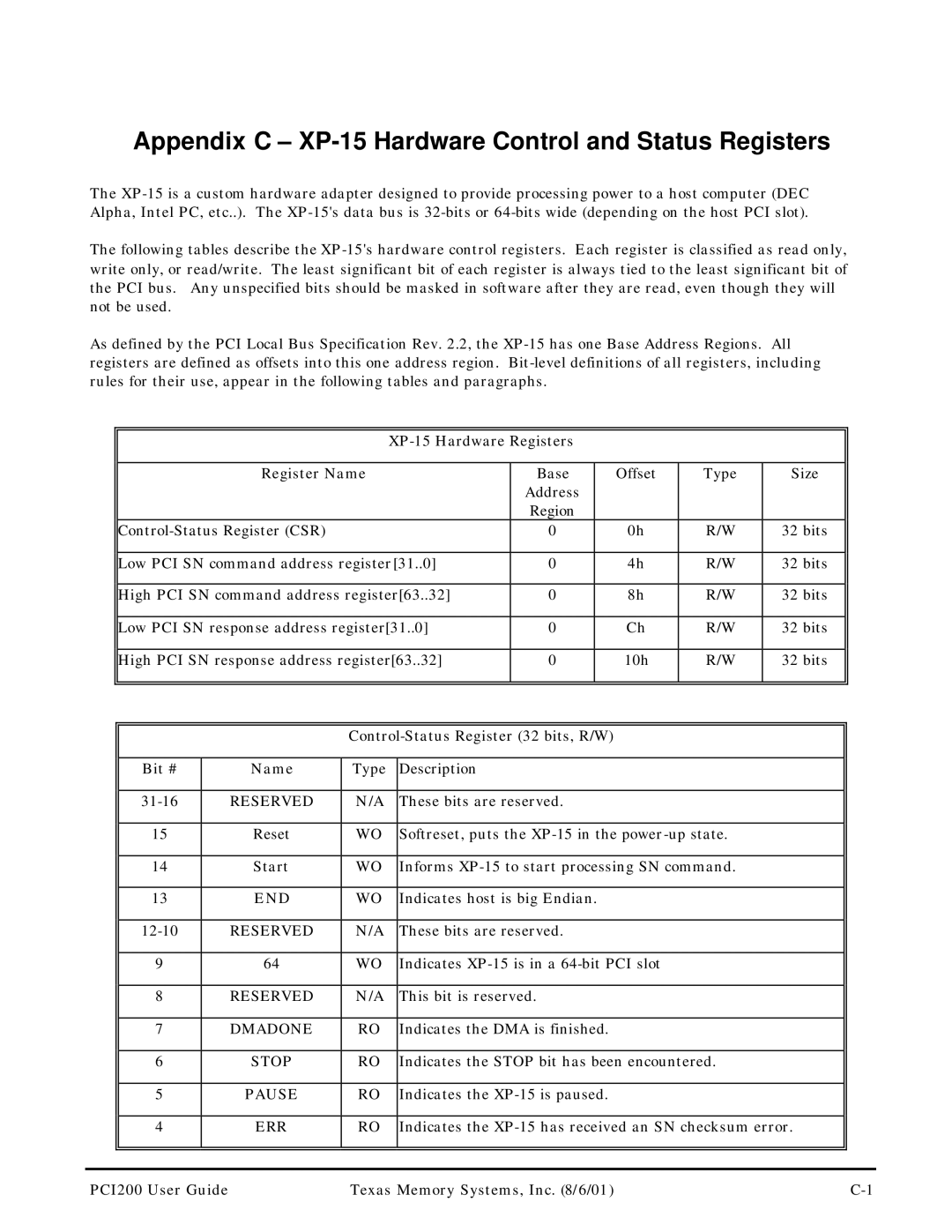

Appendix C – XP-15 Hardware Control and Status Registers

The

The following tables describe the

As defined by the PCI Local Bus Specification Rev. 2.2, the

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Register Name |

|

| Base |

| Offset | Type | Size |

| |

|

|

|

|

|

|

| Address |

|

|

|

|

|

|

|

|

|

|

|

| Region |

|

|

|

|

|

|

|

|

| 0 |

| 0h | R/W | 32 bits |

| |||

|

|

|

|

|

|

|

|

|

|

| ||

| Low PCI SN command address register[31..0] | 0 |

| 4h | R/W | 32 bits |

| |||||

|

|

|

|

|

|

|

|

|

|

| ||

| High PCI SN command address register[63..32] | 0 |

| 8h | R/W | 32 bits |

| |||||

|

|

|

|

|

|

|

|

|

|

| ||

| Low PCI SN response address register[31..0] | 0 |

| Ch | R/W | 32 bits |

| |||||

|

|

|

|

|

|

|

|

|

|

| ||

| High PCI SN response address register[63..32] | 0 |

| 10h | R/W | 32 bits |

| |||||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| Bit # |

| Name | Type |

| Description |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| RESERVED | N/A |

| These bits are reserved. |

|

|

|

| |||

|

|

|

|

|

|

|

|

| ||||

| 15 |

| Reset | WO |

| Softreset, puts the |

|

| ||||

|

|

|

|

|

|

|

|

| ||||

| 14 |

| Start | WO |

| Informs |

|

| ||||

|

|

|

|

|

|

|

|

|

|

| ||

| 13 |

| END | WO |

| Indicates host is big Endian. |

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| ||

|

| RESERVED | N/A |

| These bits are reserved. |

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| |||

| 9 |

| 64 | WO |

| Indicates |

|

|

| |||

|

|

|

|

|

|

|

|

|

|

| ||

| 8 |

| RESERVED | N/A |

| This bit is reserved. |

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| ||

| 7 |

| DMADONE | RO |

| Indicates the DMA is finished. |

|

|

|

| ||

|

|

|

|

|

|

|

|

| ||||

| 6 |

| STOP | RO |

| Indicates the STOP bit has been encountered. |

|

| ||||

|

|

|

|

|

|

|

|

|

|

| ||

| 5 |

| PAUSE | RO |

| Indicates the |

|

|

|

| ||

|

|

|

|

|

|

|

| |||||

| 4 |

| ERR | RO |

| Indicates the |

| |||||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PCI200 User Guide |

| Texas Memory Systems, Inc. (8/6/01) |

|

|

| |||||||