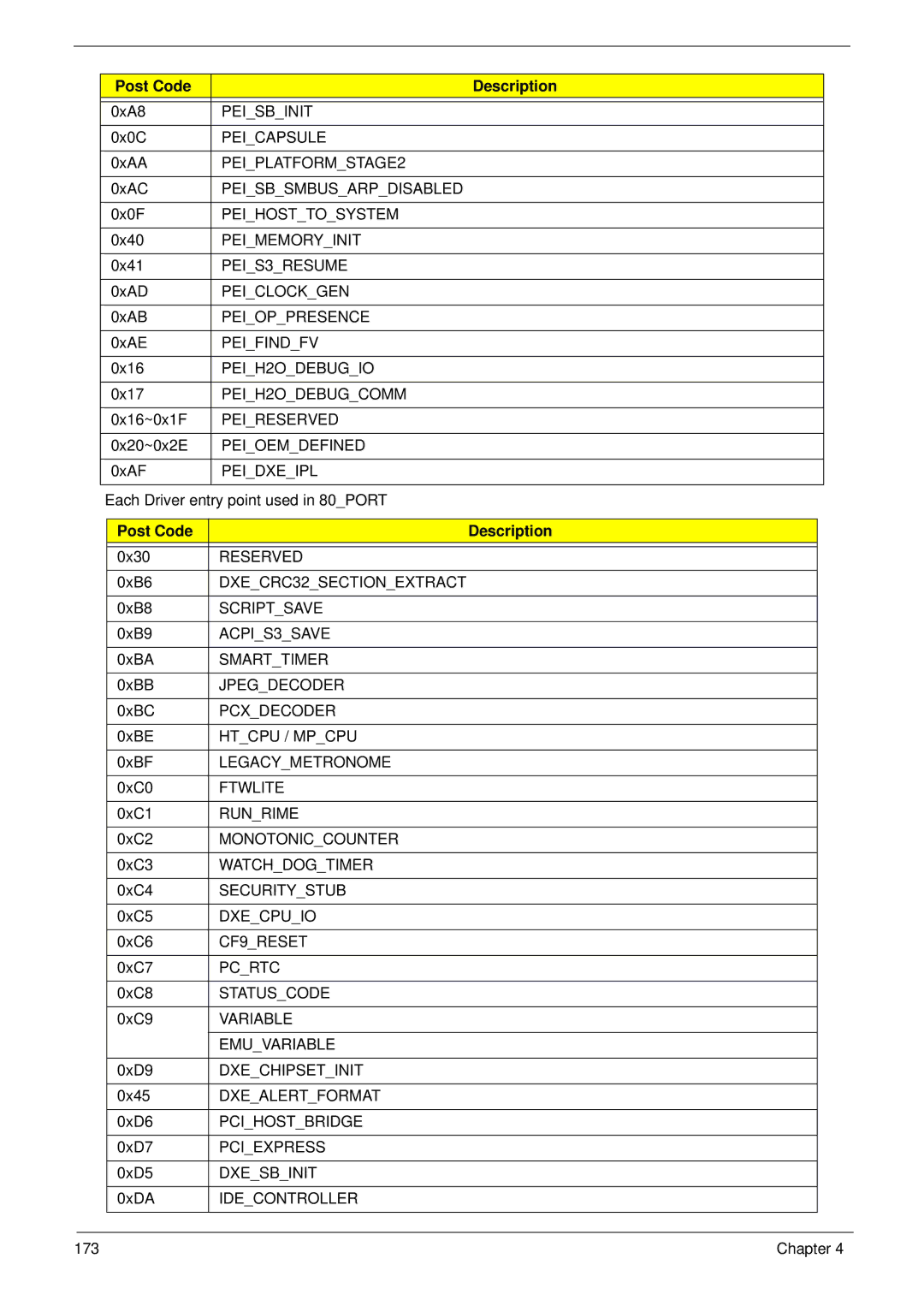

Post Code | Description |

|

|

0xA8 | PEI_SB_INIT |

0x0C | PEI_CAPSULE |

|

|

0xAA | PEI_PLATFORM_STAGE2 |

|

|

0xAC | PEI_SB_SMBUS_ARP_DISABLED |

|

|

0x0F | PEI_HOST_TO_SYSTEM |

|

|

0x40 | PEI_MEMORY_INIT |

|

|

0x41 | PEI_S3_RESUME |

|

|

0xAD | PEI_CLOCK_GEN |

|

|

0xAB | PEI_OP_PRESENCE |

|

|

0xAE | PEI_FIND_FV |

|

|

0x16 | PEI_H2O_DEBUG_IO |

|

|

0x17 | PEI_H2O_DEBUG_COMM |

|

|

0x16~0x1F | PEI_RESERVED |

|

|

0x20~0x2E | PEI_OEM_DEFINED |

|

|

0xAF | PEI_DXE_IPL |

|

|

Each Driver entry point used in 80_PORT | |

Post Code | Description |

|

|

0x30 | RESERVED |

|

|

0xB6 | DXE_CRC32_SECTION_EXTRACT |

|

|

0xB8 | SCRIPT_SAVE |

|

|

0xB9 | ACPI_S3_SAVE |

|

|

0xBA | SMART_TIMER |

|

|

0xBB | JPEG_DECODER |

|

|

0xBC | PCX_DECODER |

|

|

0xBE | HT_CPU / MP_CPU |

|

|

0xBF | LEGACY_METRONOME |

|

|

0xC0 | FTWLITE |

|

|

0xC1 | RUN_RIME |

|

|

0xC2 | MONOTONIC_COUNTER |

|

|

0xC3 | WATCH_DOG_TIMER |

|

|

0xC4 | SECURITY_STUB |

|

|

0xC5 | DXE_CPU_IO |

|

|

0xC6 | CF9_RESET |

|

|

0xC7 | PC_RTC |

|

|

0xC8 | STATUS_CODE |

|

|

0xC9 | VARIABLE |

|

|

| EMU_VARIABLE |

|

|

0xD9 | DXE_CHIPSET_INIT |

|

|

0x45 | DXE_ALERT_FORMAT |

|

|

0xD6 | PCI_HOST_BRIDGE |

|

|

0xD7 | PCI_EXPRESS |

|

|

0xD5 | DXE_SB_INIT |

|

|

0xDA | IDE_CONTROLLER |

|

|

173 | Chapter 4 |