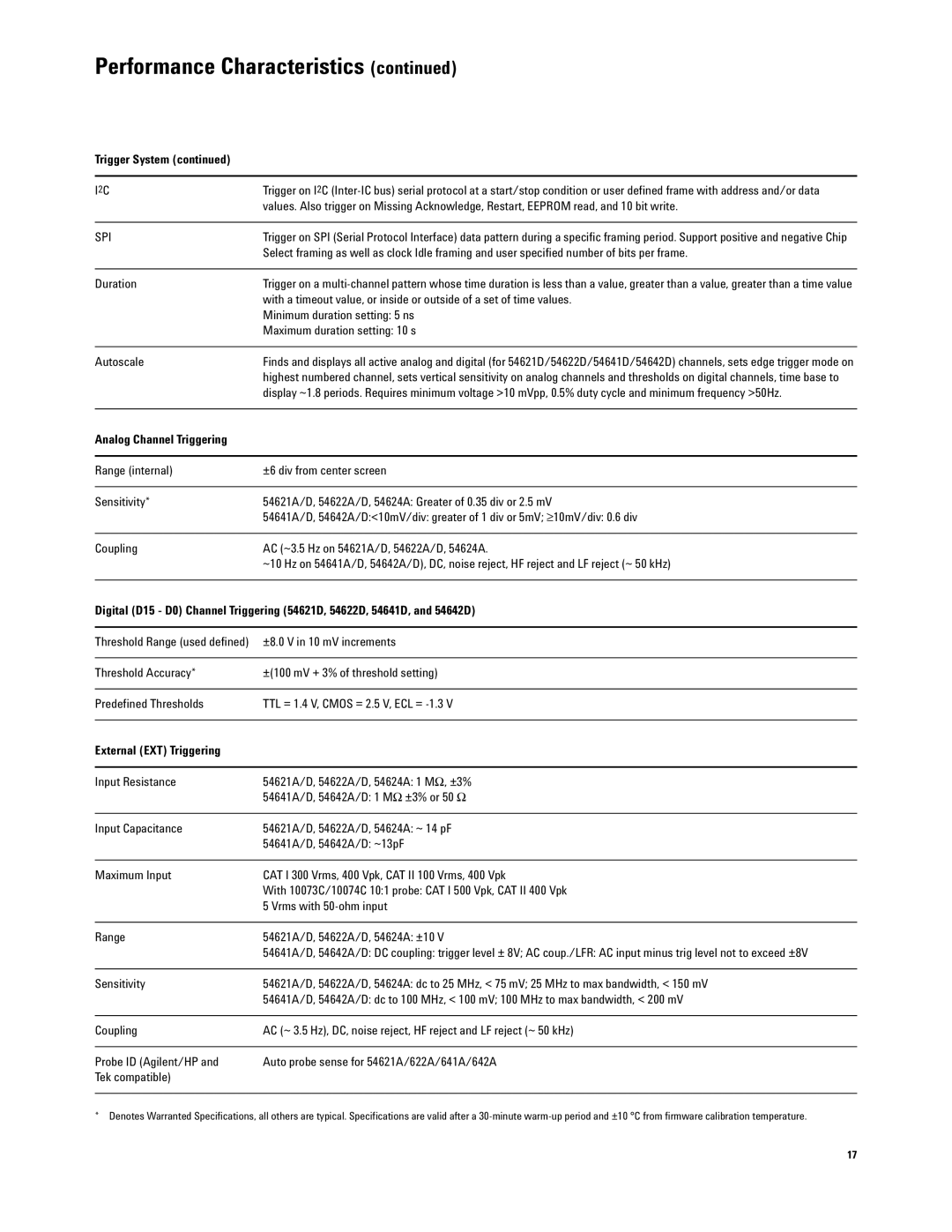

Performance Characteristics (continued)

Trigger System (continued)

I2C | Trigger on I2C |

| values. Also trigger on Missing Acknowledge, Restart, EEPROM read, and 10 bit write. |

|

|

SPI | Trigger on SPI (Serial Protocol Interface) data pattern during a specific framing period. Support positive and negative Chip |

| Select framing as well as clock Idle framing and user specified number of bits per frame. |

|

|

Duration | Trigger on a |

| with a timeout value, or inside or outside of a set of time values. |

| Minimum duration setting: 5 ns |

| Maximum duration setting: 10 s |

|

|

Autoscale | Finds and displays all active analog and digital (for 54621D/54622D/54641D/54642D) channels, sets edge trigger mode on |

| highest numbered channel, sets vertical sensitivity on analog channels and thresholds on digital channels, time base to |

| display ~1.8 periods. Requires minimum voltage >10 mVpp, 0.5% duty cycle and minimum frequency >50Hz. |

|

|

Analog Channel Triggering |

|

|

|

Range (internal) | ±6 div from center screen |

|

|

Sensitivity* | 54621A/D, 54622A/D, 54624A: Greater of 0.35 div or 2.5 mV |

| 54641A/D, 54642A/D:<10mV/div: greater of 1 div or 5mV; ≥10mV/div: 0.6 div |

|

|

Coupling | AC (~3.5 Hz on 54621A/D, 54622A/D, 54624A. |

| ~10 Hz on 54641A/D, 54642A/D), DC, noise reject, HF reject and LF reject (~ 50 kHz) |

| |

Digital (D15 - D0) Channel Triggering (54621D, 54622D, 54641D, and 54642D) | |

|

|

Threshold Range (used defined) | ±8.0 V in 10 mV increments |

|

|

Threshold Accuracy* | ±(100 mV + 3% of threshold setting) |

|

|

Predefined Thresholds | TTL = 1.4 V, CMOS = 2.5 V, ECL = |

|

|

External (EXT) Triggering |

|

|

|

Input Resistance | 54621A/D, 54622A/D, 54624A: 1 MΩ, ±3% |

| 54641A/D, 54642A/D: 1 MΩ ±3% or 50 Ω |

|

|

Input Capacitance | 54621A/D, 54622A/D, 54624A: ~ 14 pF |

| 54641A/D, 54642A/D: ~13pF |

|

|

Maximum Input | CAT I 300 Vrms, 400 Vpk, CAT II 100 Vrms, 400 Vpk |

| With 10073C/10074C 10:1 probe: CAT I 500 Vpk, CAT II 400 Vpk |

| 5 Vrms with |

|

|

Range | 54621A/D, 54622A/D, 54624A: ±10 V |

| 54641A/D, 54642A/D: DC coupling: trigger level ± 8V; AC coup./LFR: AC input minus trig level not to exceed ±8V |

|

|

Sensitivity | 54621A/D, 54622A/D, 54624A: dc to 25 MHz, < 75 mV; 25 MHz to max bandwidth, < 150 mV |

| 54641A/D, 54642A/D: dc to 100 MHz, < 100 mV; 100 MHz to max bandwidth, < 200 mV |

|

|

Coupling | AC (~ 3.5 Hz), DC, noise reject, HF reject and LF reject (~ 50 kHz) |

|

|

Probe ID (Agilent/HP and | Auto probe sense for 54621A/622A/641A/642A |

Tek compatible) |

|

|

|

* Denotes Warranted Specifications, all others are typical. Specifications are valid after a

17