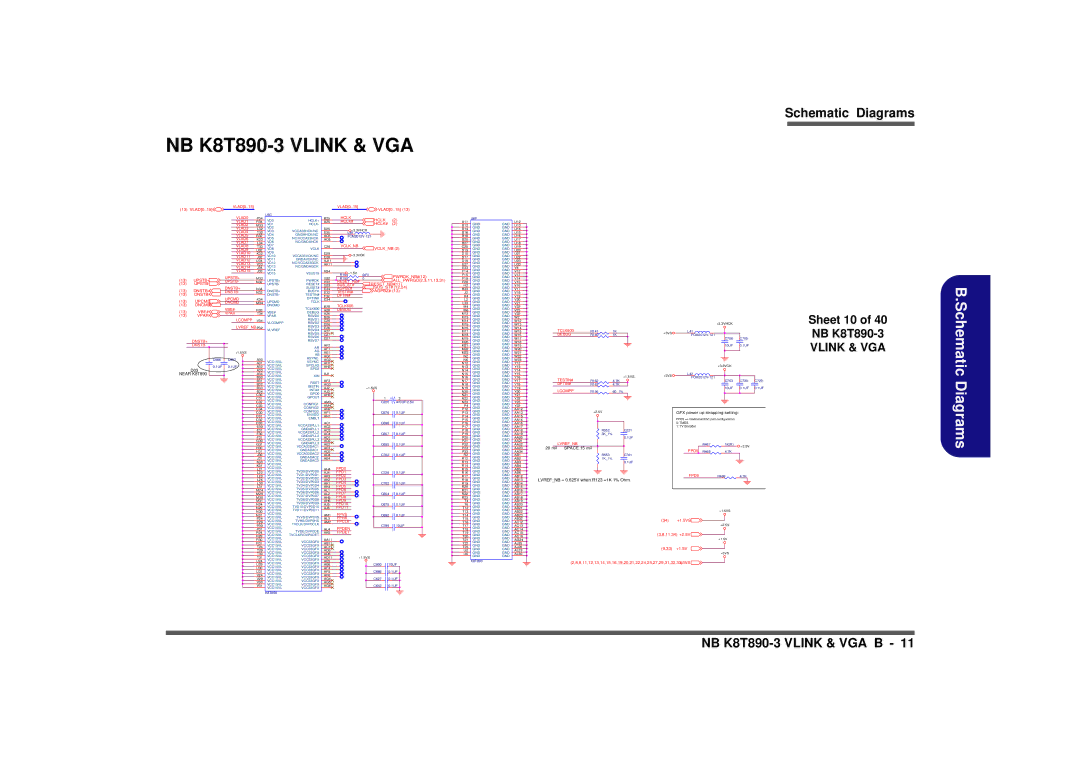

Schematic Diagrams

NB K8T890-3 VLINK & VGA

(13) VLAD[0..15] | VLAD[0..15] |

|

|

|

| VLAD[0..15] | VLAD[0..15] (13) | |||||

|

|

|

|

|

|

|

| |||||

|

| VLAD0 | P34 | U6C |

| B25 | HCLK |

|

|

|

| |

|

| VD0 | HCLK+ |

| HCLK |

| (2) | |||||

|

| VLAD1 | R34 | A25 | HCLK# |

|

| |||||

|

| VLAD2 | M33 | VD1 | HCLK- |

|

|

|

| HCLK# |

| (2) |

|

| VLAD3 | L32 | VD2 |

| D25 |

| +3.3VHCK |

|

| ||

|

| VD3 | VCCA33HCK/NC |

|

|

| ||||||

|

| VLAD4 | T32 | VD4 | GNDAHCK/NC | E25 |

| L40 |

|

|

|

|

|

| VLAD5 | R32 | AC5 | T |

|

| |||||

|

| VLAD6 | K33 | VD5 | NC/VCCA33HCK | AC6 |

|

|

|

|

| |

|

| VLAD7 | L34 | VD6 | NC/GNDAHCK |

| T |

|

|

|

|

|

|

| VLAD8 | T33 | VD7 | VCLK | C28 | VCLK_NB | VCLK_NB (2) | ||||

|

| VLAD9 | U32 | VD8 |

|

|

|

| ||||

|

| VLAD10 | K32 | VD9 | VCCA33VCK/NC | D28 |

| +3.3VCK |

|

| ||

|

| VLAD11 | J32 | VD10 | E28 |

|

|

| ||||

|

| VLAD12 | U34 | VD11 | GNDAVCK/NC | AJ11 |

|

|

|

|

|

|

|

| VLAD13 | V33 | VD12 | NC/VCCA33GCK | AK11 |

|

| T |

|

|

|

|

| VLAD14 | J34 | VD13 | NC/GNDAGCK |

|

|

| T |

|

|

|

|

| VLAD15 | J33 | VD14 | VSUS15 | H34 | R154+1.5V | 0(R) |

|

| ||

|

| UPSTB+ | M32 | VD15 | G32 |

| PWROK_NB#(12) | |||||

(13) | UPSTB+ | UPSTB+ | PWROK | R155 |

| 0 |

| |||||

UPSTB- | N32 | H32 | RESET_NB# |

|

| ALL_PWRGD(2,3,11,13,31) | ||||||

(13) | UPSTB- |

|

| UPSTB- | RESET# | G33 | SUS_ST# |

| RESET_NB#(11) | |||

(13) | DNSTB+ | DNSTB+ | N34 |

| SUSST# | E34 | AGPBZ# |

| SUS_ST# (12,24) | |||

DNSTB- | N33 | DNSTB+ | BUSY# | E32 | TESTIN# |

| AGPBZ# (13) | |||||

(13) | DNSTB- | UPCMD |

| DNSTB- | TESTIN# | F32 | DFTIN# |

|

|

|

| |

(13) | UPCMD | K34 |

| DFTIN# | D34 |

|

|

|

|

|

| |

DNCMD | M34 | UPCMD | TCLK |

| T |

|

|

|

| |||

(13) | DNCMD | VBE# |

| DNCMD | TCLK600 | B28 | TCLK600 |

|

|

|

| |

(13) | VBE# | R33 |

| A28 | DEBUG |

|

|

|

| |||

VPAR | T34 | VBE# | DEBUG | A26 | T |

|

|

|

|

| ||

(13) | VPAR |

|

| VPAR | RSVD0 | B26 |

|

|

|

|

| |

|

| LCOMPP | V34 | VLCOMPP | RSVD1 | C26 | T |

|

|

|

|

|

|

|

|

| RSVD2 | D26 | T |

|

|

|

|

| |

|

| LVREF_NB P32 | VLVREF | RSVD3 | E26 | T |

|

|

|

|

| |

|

|

|

| RSVD4 | A27 | T |

|

|

|

|

| |

|

|

|

|

| RSVD5 | C27 |

|

|

|

|

|

|

|

|

|

|

| RSVD6 | D27 | T |

|

|

|

|

|

| DNSTB+ |

|

|

| RSVD7 | T |

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| |||

| DNSTB- |

|

|

| AR | AF2 | T |

|

|

|

|

|

|

|

|

|

| AF1 |

|

|

|

|

| ||

|

|

|

|

| AG | T |

|

|

|

|

| |

|

| +1.5VS |

|

| AE1 |

|

|

|

|

| ||

|

|

|

|

| AB | AG1 | T |

|

|

|

|

|

|

|

|

|

| HSYNC | T |

|

|

|

|

| |

| C986 | C987 | A30 |

| AG2 |

|

|

|

|

| ||

| VCC15VL | VSYNC |

|

|

|

|

|

| ||||

|

|

| A31 | AH1 |

|

|

|

|

|

| ||

| 0.1UF | 0.1UF | VCC15VL | SPCLK2 |

|

|

|

|

|

| ||

| A32 | AH2 |

|

|

|

|

|

| ||||

| VCC15VL | SPD2 |

|

|

|

|

|

| ||||

| D03 |

| A33 |

|

|

|

|

|

|

| ||

|

| A34 | VCC15VL |

| AJ1 |

|

|

|

|

|

| |

NEAR K8T890 |

| VCC15VL | XIN |

|

|

|

|

|

| |||

| B30 |

|

|

|

|

|

|

| ||||

|

|

| VCC15VL |

|

|

|

|

|

|

|

| |

|

|

| B31 |

| AF3 |

|

|

|

|

|

| |

|

|

| VCC15VL | RSET | T |

|

|

|

|

| ||

|

|

| B32 | AG3 |

|

|

|

|

| |||

|

|

| VCC15VL | BISTIN | T |

|

|

|

|

| ||

|

|

| B33 | AJ2 |

|

| +1.5VS |

|

| |||

|

|

| B34 | VCC15VL | INTA# | AJ3 |

|

|

|

|

|

|

|

|

| VCC15VL | GPO0 |

|

|

|

|

|

| ||

|

|

| C30 | AH3 |

|

|

|

|

|

| ||

|

|

| C31 | VCC15VL | GPOUT |

|

|

|

| 1 | + | 2 |

|

|

| VCC15VL |

|

|

|

|

|

| |||

|

|

| C32 |

| AM3 |

|

|

| C220 | 470UF/2.5V | ||

|

|

| VCC15VL | CONFIG1 |

|

|

| |||||

|

|

| C33 | AM4 |

|

|

|

|

|

| ||

|

|

| C34 | VCC15VL | CONFIG2 | AN2 |

|

|

|

|

|

|

|

|

| VCC15VL | CONFIG3 | T |

|

|

|

|

| ||

|

|

| D30 | AP1 |

|

| C676 | 0.1UF | ||||

|

|

| D31 | VCC15VL | ENVDD | AN1 | T |

|

|

|

|

|

|

|

| VCC15VL | ENBLT | T |

|

|

|

|

| ||

|

|

| D32 |

|

|

|

|

|

| |||

|

|

| VCC15VL |

|

|

|

|

|

|

|

| |

|

|

| D33 |

| AC1 |

|

|

| C698 | 0.1UF | ||

|

|

| E30 | VCC15VL | VCCA33PLL1 | AC2 | T |

|

|

|

|

|

|

|

| VCC15VL | GNDAPLL1 | T |

|

|

|

|

| ||

|

|

| E31 | AC3 |

|

|

|

|

| |||

|

|

| F30 | VCC15VL | VCCA33PLL2 | AC4 | T |

|

| C657 | 0.1UF | |

|

|

| VCC15VL | GNDAPLL2 | T |

|

| |||||

|

|

| F31 | AD1 |

|

|

|

|

| |||

|

|

| VCC15VL | VCCA33PLL3 | T |

|

|

|

|

| ||

|

|

| G30 | AD2 |

|

|

|

|

| |||

|

|

| VCC15VL | GNDAPLL3 |

|

|

|

|

|

| ||

|

|

| G31 | AE2 |

|

|

| C655 | 0.1UF | |||

|

|

| VCC15VL | VCCA33DAC1 | T |

|

| |||||

|

|

| H30 | AE3 |

|

|

|

|

| |||

|

|

| H31 | VCC15VL | GNDADAC1 | AD3 |

|

|

|

|

|

|

|

|

| VCC15VL | VCCA33DAC2 | T |

|

|

|

|

| ||

|

|

| J30 | AD4 |

|

| C762 | 0.1UF | ||||

|

|

| VCC15VL | GNDADAC2 | T |

|

| |||||

|

|

| J31 | AE4 |

|

|

|

|

| |||

|

|

| VCC15VL | GNDADAC3 | T |

|

|

|

|

| ||

|

|

| K30 |

|

|

|

|

|

| |||

|

|

| VCC15VL |

|

|

|

|

|

|

|

| |

|

|

| K31 |

|

|

|

|

|

|

|

| |

|

|

| L21 | VCC15VL |

| AH4 | FPD0 |

|

|

|

|

|

|

|

| L22 | VCC15VL | TVD0/DVP0D0 | AJ4 | FPD1 |

|

| C728 | 0.1UF | |

|

|

| L23 | VCC15VL | TVD1/DVP0D1 | AK3 | FPD2 |

|

|

|

|

|

|

|

| L24 | VCC15VL | TVD2/DVP0D2 | AK2 | FPD3 |

|

|

|

|

|

|

|

| L30 | VCC15VL | TVD3/DVP0D3 | AK1 | FPD4 |

| T | C702 | 0.1UF | |

|

|

| L31 | VCC15VL | TVD4/DVP0D4 | AK4 | FPD5 |

| T |

|

|

|

|

|

| M24 | VCC15VL | TVD5/DVP0D5 | AL1 | FPD6 |

|

|

|

|

|

|

|

| M29 | VCC15VL | TVD6/DVP0D6 | AL2 | FPD7 |

| T | C654 | 0.1UF | |

|

|

| M30 | VCC15VL | TVD7/DVP0D7 | AH5 | FPD8 |

| T |

|

|

|

|

|

| M31 | VCC15VL | TVD8/DVP0D8 | AH6 | FPD9 |

|

|

|

|

|

|

|

| N24 | VCC15VL | TVD9/DVP0D9 | AJ5 | FPD10 |

| C675 | 0.1UF | ||

|

|

| N29 | VCC15VL | TVD10/DVP0D10 | AJ6 | FPD11 |

|

|

|

| |

|

|

| N30 | VCC15VL | TVD11/DVP0D11 |

|

|

|

|

|

|

|

|

|

| VCC15VL |

|

| FPVS |

|

|

|

|

| |

|

|

| N31 |

| AM1 |

|

| C692 | 0.1UF | |||

A11 |

| U6F |

|

| U12 |

| GND | GND |

| ||

B12 |

| U13 | |||

GND | GND |

| |||

B14 |

| U14 | |||

GND | GND |

| |||

B16 |

| U15 | |||

GND | GND |

| |||

B18 |

| U16 | |||

GND | GND |

| |||

B20 |

| U17 | |||

B27 | GND | GND |

| U18 | |

GND | GND |

| |||

C25 |

| U19 | |||

GND | GND |

| |||

D13 |

| U20 | |||

GND | GND |

| |||

D15 |

| U21 | |||

GND | GND |

| |||

D17 |

| U22 | |||

D19 | GND | GND |

| U23 | |

GND | GND |

| |||

E27 |

| U33 | |||

GND | GND |

| |||

E33 |

| V4 | |||

GND | GND |

| |||

F14 |

| V12 | |||

GND | GND |

| |||

F15 |

| V13 | |||

GND | GND |

| |||

F19 |

| V14 | |||

GND | GND |

| |||

F20 |

| V15 | |||

H2 | GND | GND |

| V16 | |

GND | GND |

| |||

H33 |

| V17 | |||

GND | GND |

| |||

J2 |

| V18 | |||

GND | GND |

| |||

K4 |

| V19 | |||

GND | GND |

| |||

L2 |

| V20 | |||

L33 | GND | GND |

| V21 | |

GND | GND |

| |||

M4 |

| V22 | |||

GND | GND |

| |||

M6 |

| V23 | |||

GND | GND |

| |||

M12 |

| V32 | |||

GND | GND |

| |||

M13 |

| W2 | |||

M14 | GND | GND |

| W12 | |

GND | GND |

| |||

M15 |

| W13 | |||

GND | GND |

| |||

M16 |

| W14 | |||

GND | GND |

| |||

M17 |

| W15 | |||

GND | GND |

| |||

M18 |

| W16 | |||

M19 | GND | GND |

| W17 | |

GND | GND |

| |||

M20 |

| W18 | |||

GND | GND |

| |||

M21 |

| W19 | |||

GND | GND |

| |||

M22 |

| W20 | |||

GND | GND |

| |||

M23 |

| W21 | |||

N2 | GND | GND |

| W22 | |

GND | GND |

| |||

N6 |

| W23 | |||

N12 | GND | GND |

| Y12 | |

GND | GND |

| |||

N13 |

| Y13 | |||

GND | GND |

| |||

N14 |

| Y14 | |||

N15 | GND | GND |

| Y15 | |

GND | GND |

| |||

N16 |

| Y16 | |||

N17 | GND | GND |

| Y17 | |

GND | GND |

| |||

N18 |

| Y18 | |||

GND | GND |

| |||

N19 |

| Y19 | |||

GND | GND |

| |||

N20 |

| Y20 | |||

GND | GND |

| |||

N21 |

| Y21 | |||

N22 | GND | GND |

| Y22 | |

GND | GND |

| |||

N23 |

| Y23 | |||

GND | GND |

| |||

P4 |

| Y32 | |||

GND | GND |

| |||

P12 |

| AA12 | |||

GND | GND |

| |||

P13 |

| AA13 | |||

P14 | GND | GND |

| AA15 | |

GND | GND |

| |||

P15 |

| AA14 | |||

GND | GND |

| |||

P16 |

| AA16 | |||

GND | GND |

| |||

P17 |

| AA17 | |||

GND | GND |

| |||

P18 |

| AA18 | |||

P19 | GND | GND |

| AA19 | |

GND | GND |

| |||

P20 |

| AA20 | |||

GND | GND |

| |||

P21 |

| AA21 | |||

GND | GND |

| |||

P22 |

| AA22 | |||

GND | GND |

| |||

P23 |

| AA23 | |||

P33 | GND | GND |

| AA34 | |

GND | GND |

| |||

R2 |

| AB1 | |||

GND | GND |

| |||

R12 |

| AB2 | |||

GND | GND |

| |||

R13 |

| AB3 | |||

GND | GND |

| |||

R14 |

| AB4 | |||

GND | GND |

| |||

R15 |

| AB5 | |||

GND | GND |

| |||

R16 |

| AB6 | |||

R17 | GND | GND |

| AB12 | |

GND | GND |

| |||

R18 |

| AB13 | |||

GND | GND |

| |||

R19 |

| AB14 | |||

GND | GND |

| |||

R20 |

| AB15 | |||

GND | GND |

| |||

R21 |

| AB16 | |||

R22 | GND | GND |

| AB17 | |

GND | GND |

| |||

R23 |

| AB18 | |||

GND | GND |

| |||

T4 |

| AB19 | |||

GND | GND |

| |||

T6 |

| AB20 | |||

GND | GND |

| |||

T12 |

| AB21 | |||

T13 | GND | GND |

| AB22 | |

GND | GND |

| |||

T14 |

| AB23 | |||

|

|

| |||

TCLK600 R141 1K

DEBUG R140 1K

+1.5VS

TESTIN# R162 4.7K

DFTIN# R163 4.7K

LCOMPP R156 60_1%

+2.5V

R552 C221

3K_1% ![]() 0.1UF

0.1UF

LVREF_NB

20 mil SPACE 15 mil ![]()

R553 C761

1K_1% ![]() 0.1UF

0.1UF

LVREF_NB = 0.625V when R123 =1K 1% Ohm

| +3.3VHCK |

|

|

+3VS | L41 |

|

|

|

| ||

| C706 | C705 |

|

| 10UF | 0.1UF |

|

| +3.3VCK |

|

|

+3VS | L42 |

|

|

|

| ||

| C763 | C730 | C729 |

| 10UF | 0.1UF | 0.1UF |

GFX power up strapping setting:

FPD5 => Dedicated DVI port configuration

0:TMDS

1:TV Encoder

R467 | 1K(R) | +2.5V |

|

| |

FPD5 R468 | 4.7K |

|

FPD9 | R469 | 4.7K |

| +1.5VS |

|

Sheet 10 of 40 NB K8T890-3

VLINK & VGA

B.Schematic Diagrams

P24 | VCC15VL | TVVS/DVP0VS | AL3 | FPHS | T |

|

|

|

P29 | VCC15VL | TVHS/DVP0HS | AM2 | FPCLK | T |

|

|

|

P30 | VCC15VL | TVCLK/DVP0CLK |

|

| C799 | 10UF | ||

P31 | VCC15VL | TVDE/DVP0DE | AL4 | FPDEN |

|

|

|

|

R24 | VCC15VL | AK5 | FPDET |

|

|

|

| |

R29 | VCC15VL | TVCLKR/DVP0DET |

|

|

|

|

|

|

VCC15VL |

|

|

|

|

|

|

| |

R30 |

| AA11 |

|

|

|

|

| |

VCC15VL | VCC33GFX | T |

|

|

|

| ||

R31 | AB11 |

|

|

|

| |||

T24 | VCC15VL | VCC33GFX | AC11 |

|

|

|

|

|

VCC15VL | VCC33GFX |

|

|

|

|

| ||

T29 | AD5 |

|

|

|

|

| ||

VCC15VL | VCC33GFX | T |

|

|

|

| ||

T30 | AD6 |

|

|

|

| |||

VCC15VL | VCC33GFX | T |

|

|

|

| ||

T31 | AD11 | +1.5VS |

|

|

| |||

VCC15VL | VCC33GFX | T |

|

|

| |||

U24 | AE5 |

|

|

|

| |||

U29 | VCC15VL | VCC33GFX | AE6 | T |

| C800 | 10UF | |

VCC15VL | VCC33GFX | T |

| |||||

U30 | AF4 |

|

|

|

| |||

VCC15VL | VCC33GFX | T |

|

|

|

| ||

U31 | AF5 |

| C666 | 0.1UF | ||||

VCC15VL | VCC33GFX | T |

| |||||

V24 | AF6 |

|

|

|

| |||

VCC15VL | VCC33GFX | T |

|

|

|

| ||

V29 | AG4 |

| C627 | 0.1UF | ||||

V30 | VCC15VL | VCC33GFX | AG5 |

|

|

|

|

|

VCC15VL | VCC33GFX |

|

|

|

|

| ||

V31 | AG6 |

|

| C642 | 0.1UF | |||

VCC15VL | VCC33GFX |

|

| |||||

|

|

|

|

|

|

| ||

| K8T890 |

|

|

|

|

|

|

|

T15 | GND | GND |

| AB32 |

| |

GND | GND |

| ||||

T16 |

| AC12 |

| |||

GND | GND |

| ||||

T17 |

| AC13 | ||||

T18 | GND | GND |

| AC14 |

| |

GND | GND |

| ||||

T19 |

| AC15 |

| |||

GND | GND |

| ||||

T20 |

| AC16 |

| |||

GND | GND |

| ||||

T21 |

| AG34 | ||||

GND | GND |

| ||||

T22 |

| AJ25 |

| |||

T23 | GND | GND |

| AJ28 |

| |

GND | GND |

| ||||

U2 |

| AL29 | ||||

U6 | GND | GND |

| AL30 |

| |

GND | GND |

| ||||

|

|

|

|

| ||

|

| K8T890 |

|

|

|

|

(34) +1.5VS![]()

+2.5V

(3,8,11,34) +2.5V![]()

+1.5V

(9,33) +1.5V

+3VS

(2,8,9,11,12,13,14,15,16,19,20,21,22,24,25,27,29,31,32,33)+3VS![]()

NB