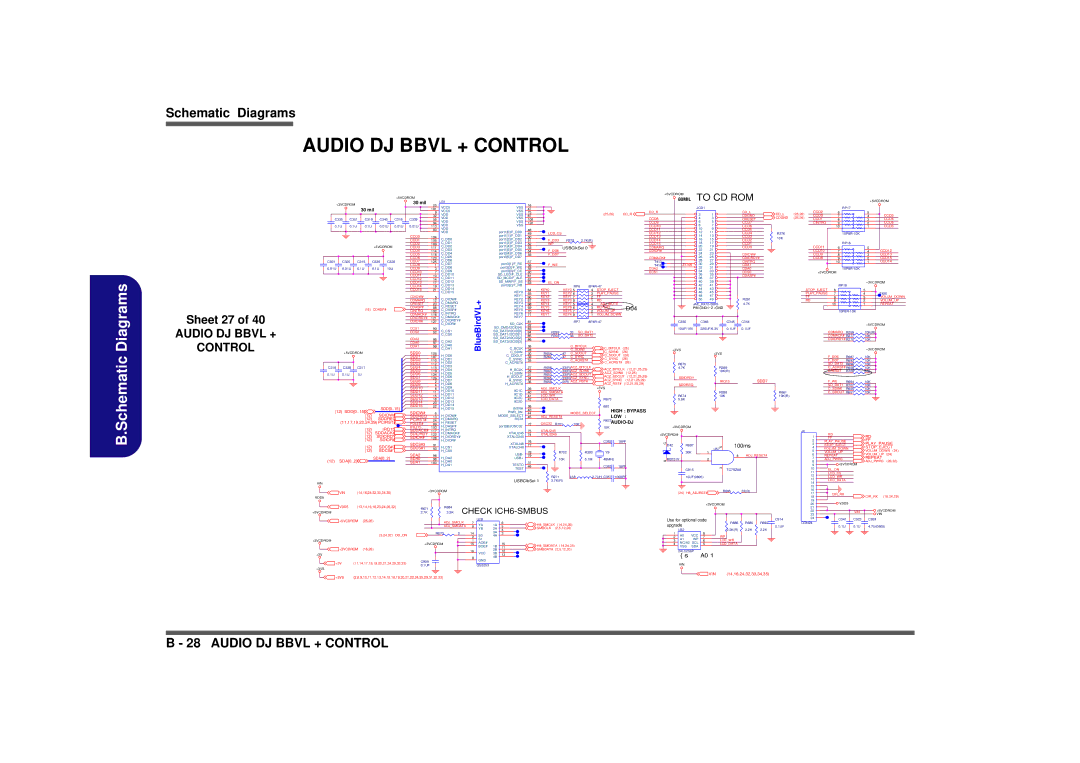

Schematic Diagrams

AUDIO DJ BBVL + CONTROL

B.Schematic Diagrams

Sheet 27 of 40

AUDIO DJ BBVL +

CONTROL

|

|

|

|

|

|

| +5VCDROM |

|

|

|

|

|

|

|

|

|

|

|

|

| |

+3VCDROM |

|

|

|

|

|

| 30 mil | 25 | U31 |

|

| 16 |

|

|

|

|

|

|

|

| |

|

|

|

|

|

| VCC5 |

| VSS |

|

|

|

|

|

|

|

| |||||

|

| 30 mil |

|

|

|

| 101 |

| 47 |

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

| VCC5 |

| VSS |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

| 9 |

| 73 |

|

|

|

|

| (25,26) | CD_R | ||||||

|

|

|

|

|

|

|

|

| 32 | VDD |

| VSS | 87 |

|

|

|

|

| |||

C335 | C351 | C319 | C340 | C316 | C339 | VDD |

| VSS |

|

|

|

|

|

|

|

| |||||

56 |

| 108 |

|

|

|

|

|

|

|

| |||||||||||

VDD |

| VSS |

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

| 94 |

| 120 |

|

|

|

|

|

|

|

| ||

0.1U | 0.1U |

| 0.1U |

| 0.01U | 0.01U | 0.01U | VDD |

| VSS |

|

|

|

|

|

|

|

| |||

|

| 113 |

|

|

|

|

|

|

|

|

|

| |||||||||

|

| VDD |

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

| 80 |

|

| 48 |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| VDD |

| port1[0]/F_DD0 | 49 | LCD_CS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CCD0 | 104 |

|

| port1[1]/F_DD1 |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

| 50 |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

| CCD1 | 106 | C_DD0 |

| port1[2]/F_DD2 | 51 | F_DD3 |

| R278 |

| 2.7K(R) |

|

|

|

|

|

|

|

|

|

|

| CCD2 | 109 | C_DD1 |

| port1[3]/F_DD3 | 52 | WP |

|

|

|

|

|

|

|

|

|

|

| +3VCDROM |

| CCD3 | 111 | C_DD2 |

| port1[4]/F_DD4 | 53 |

| USBClkSel 0 |

|

|

| |||||

|

|

|

|

| C_DD3 |

| port1[5]/F_DD5 | F_DD6 |

|

|

| ||||||||||

|

|

|

|

|

|

|

| CCD4 | 114 |

| 54 |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

| CCD5 | 118 | C_DD4 |

| port3[4]/F_DD6 | 55 | F_DD7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CCD6 | 123 | C_DD5 |

| port3[5]/F_DD7 |

|

|

|

|

|

|

|

|

|

C931 | C325 | C315 | C336 | C320 | CCD7 | 125 | C_DD6 |

| port3[1]/F_RE | 57 | F_WE |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

| CCD8 | 1 | C_DD7 |

| 58 |

|

|

|

|

|

|

| ||

0.01U | 0.01U | 0.1U |

| 0.1U |

| 10U |

| CCD9 | 3 | C_DD8 |

| port3[3]/F_WE | 59 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CCD10 | 7 | C_DD9 |

| port3[0]/F_CE | 60 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CCD11 | 10 | C_DD10 |

| SD_LED/F_CLE | 61 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CCD12 | 14 | C_DD11 |

| SD_MCD/F_ALE | 62 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CCD13 | 17 | C_DD12 |

| SD_MWP/F_SE | 63 | EL_ON |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CCD14 | 19 | C_DD13 |

| port3[2]/F_RB | 64 | KEY0 |

| RP6 |

|

| |||

|

|

|

|

|

|

|

| CCD15 | 21 | C_DD14 |

|

| KEY3 5 |

| 4 | STOP_EJECT |

|

| |||

|

|

|

|

|

|

|

|

|

| C_DD15 |

| KEY0 | 65 | KEY1 | KEY2 6 |

| 3 | PLAY_PAUSE |

|

| |

|

|

|

|

|

|

|

| CDIOW# | 5 |

| BlueBirdVL+ | KEY1 | 66 | KEY2 | KEY1 7 |

| 2 | FF |

|

| |

|

|

|

|

|

|

|

| CDMARQ | 12 | C_DIOW# | KEY2 | 67 | KEY3 | KEY0 8 |

| 1 | RD |

|

| ||

|

|

|

|

|

|

|

| CRESET | 23 | C_DMARQ | KEY3 | 68 | KEY4 | KEY7 5 |

| 4 | ADJ_MUTE |

|

| ||

|

|

| (16) CDASP# |

| CDASP# | 88 | C_RESET | KEY4 | 69 | KEY5 | KEY6 6 |

| 3 | REPEAT |

| D04 | |||||

|

|

|

| CINTRQ | 102 | C_DASP# | KEY5 | 70 | KEY6 | KEY5 7 |

| 2 | VOLUM_UP |

| |||||||

|

|

|

|

|

|

|

| CDMACK# | 116 | C_INTRQ | KEY6 | 71 | KEY7 | KEY4 8 |

| 1 | VOLUM_DOWN |

|

| ||

|

|

|

|

|

|

|

| CDIORDY# | 121 | C_DMACK# | KEY7 |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| CDIOR# | 127 | C_DIORDY# | SD_CLK | 81 |

|

| RP7 |

|

| ||||

|

|

|

|

|

|

|

|

|

| C_DIOR# | 82 |

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

| CCS1 | 90 |

| SD_CMD/I2CID[4] | 83 |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| CCS0 | 92 | C_CS1 | SD_DAT0/I2CID[0] | 84 | R299 |

| 33 | SD_DAT1 |

|

|

| ||

|

|

|

|

|

|

|

|

|

| C_CS0 | SD_DAT1/I2CID[1] | 85 | R703 |

| 33 | SD_DAT2 |

|

|

| ||

|

|

|

|

|

|

|

| CDA2 | 95 |

| SD_DAT2/I2CID[2] | 86 |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| CDA0 | 97 | C_DA2 | SD_DAT3/I2CID[3] |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| CDA1 | 99 | C_DA0 |

| 26 |

|

| C_BITCLK | C_BITCLK | (26) | ||||

| +5VCDROM |

|

|

|

|

| SDD0 | 105 | C_DA1 | C_BCLK | 28 | R654 | 47 | C_SDIN0 | |||||||

|

|

|

|

|

|

|

| C_SDIN | 30 | C_SDOUT | C_SDIN0 | (26) | |||||||||

|

|

|

|

|

|

|

| SDD1 | 107 | H_DD0 |

| C_CDOUT | 33 | R264 | 47 | C_SYNC | C_SDOUT | (26) | |||

|

|

|

|

|

|

|

| SDD2 | 110 | H_DD1 |

| C_SYNC | 35 |

|

| C_ACRST# | C_SYNC | (26) | |||

|

|

|

|

|

|

|

| SDD3 | 112 | H_DD2 |

| C_ACRST# |

|

|

|

|

|

| C_ACRST# | (26) | |

C318 | C338 | C317 |

|

|

|

| SDD4 | 115 | H_DD3 |

|

| 27 | R656 | 33(R)ACZ_BITCLK | ACZ_BITCLK | (12,21,25,29) | |||||

|

|

|

|

|

|

|

| SDD5 | 119 | H_DD4 |

| H_BCLK | 29 | R660 | 33(R)ACZ_SDIN0 | ||||||

0.1U | 0.1U | 1U |

|

|

|

|

| SDD6 | 124 | H_DD5 |

| H_SDIN | 31 | R653 | 33(R)ACZ_SDOUT | ACZ_SDIN0 | (12,25) | ||||

|

|

|

|

|

|

|

| SDD7 | 126 | H_DD6 |

| H_SDOUT | 34 | R265 | 33(R)ACZ_SYNC | ACZ_SDOUT | (12,21,25,29) | ||||

|

|

|

|

|

|

|

| SDD8 | 2 | H_DD7 |

| H_SYNC | 36 | R659 | 0(R) ACZ_RST# | ACZ_SYNC | (12,21,25,29) | ||||

|

|

|

|

|

|

|

| SDD9 | 4 | H_DD8 |

| H_ACRST# |

|

|

|

|

|

| ACZ_RST# | (12,21,25,29) | |

|

|

|

|

|

|

|

| SDD10 | 8 | H_DD9 |

|

| 39 | ADJ_SMCLK |

|

|

|

| +3VS |

|

|

|

|

|

|

|

|

|

| SDD11 | 11 | H_DD10 |

| IIC1C | 40 | ADJ_SMDATA |

|

|

|

|

|

| |

|

|

|

|

|

|

|

| SDD12 | 15 | H_DD11 |

| IIC1D | 41 | LCD_WR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| SDD13 | 18 | H_DD12 |

| IIC2C | 42 | LCD_DATA |

|

|

|

| R673 |

|

|

|

|

|

|

|

|

|

| SDD14 | 20 | H_DD13 |

| IIC2D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| SDD[0..15] | SDD15 | 22 | H_DD14 |

| INTR# | 38 |

|

|

|

|

| 680 |

|

| |

(12) SDD[0..15] |

|

|

|

| H_DD15 |

| 43 |

|

|

|

|

| HIGH : BYPASS | ||||||||

|

|

|

| SDIOW# | 6 |

|

| PWR_DN | 44 |

|

| MODE_SELECT | |||||||||

|

|

| (12) | SDIOW# | H_DIOW# |

| MODE_SELECT |

|

| LOW : | |||||||||||

|

|

| SDDREQ | 13 |

| 45 | ADJ_RESET# |

|

|

|

| ||||||||||

|

|

| (12) | SDDREQ | PCIRST# | 24 | H_DMARQ |

| RST# |

| OSC32 R701 |

|

|

| R672 |

|

| ||||

(11,17,19,22,24,29) PCIRST# | PDLED# | 89 | H_RESET |

|

| 72 | 10K |

| |||||||||||||

| +5VCDROM | TO CD ROM |

|

|

|

|

|

|

| |||

| 80MIL |

|

|

|

|

| +5VCDROM | |||||

|

| JCD1 |

|

|

|

|

| CCD2 | RP17 |

|

| |

CD_R |

| 2 | 1 |

| CD_L | CD_L | (25,26) | 6 |

| 5 | CCD3 | |

CCD8 |

|

| CDGND | CCD0 | 7 |

| 4 | |||||

| 4 | 3 |

| CRESET | CDGND | (25,26) | CCD1 | 8 |

| 3 | CCD4 | |

CCD9 |

| 6 | 5 |

| CCD7 |

|

| CINTRQ | 9 |

| 2 | CCD5 |

CCD10 |

| 8 | 7 |

| CCD6 |

|

|

| 10 |

| 1 | CCD6 |

CCD11 |

| 10 | 9 |

| CCD5 |

|

|

|

|

|

|

|

CCD12 |

| 12 | 11 |

| CCD4 | R276 |

|

|

|

| ||

CCD13 |

| 14 | 13 |

| CCD3 | 10K |

|

|

|

|

|

|

CCD14 |

| 16 | 15 |

| CCD2 |

|

|

|

|

|

| |

CCD15 |

| 18 | 17 |

| CCD1 |

|

| CCD11 | RP16 |

|

| |

CDMARQ |

| 20 | 19 |

| CCD0 |

|

| 6 |

| 5 | CCD12 | |

CDIOR# |

| 22 | 21 |

|

|

|

| CCD10 | 7 |

| 4 | |

|

| 24 | 23 |

| CDIOW# |

|

| CCD9 | 8 |

| 3 | CCD13 |

CDMACK# | 26 | 25 |

| CDIORDY# |

|

| CCD8 | 9 |

| 2 | CCD15 | |

T413 |

| 28 | 27 |

| CINTRQ |

|

|

| 10 |

| 1 | CCD14 |

T418 | Z1709 | 30 | 29 |

| CDA1 |

|

|

|

|

|

|

|

CDA2 |

| 32 | 31 |

| CDA0 |

|

|

|

|

| ||

CCS1 |

| 34 | 33 |

| CCS0 |

|

| +5VCDROM |

|

|

| |

| 36 | 35 |

|

|

|

|

|

| ||||

|

|

| CDASP# |

|

|

|

|

|

|

| ||

|

| 38 | 37 |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| ||

|

| 40 | 39 |

|

|

|

|

| RP18 | +3VCDROM | ||

|

| 42 | 41 |

|

|

|

|

|

|

| ||

|

| 44 | 43 |

|

|

|

| STOP_EJECT | 6 |

| 5 |

|

|

| 46 | 45 |

|

|

|

| PLAY_PAUSE | 7 |

| 4 | T420 |

|

| 48 | 47 |

|

|

|

| FF | 8 |

| 3 | VOLUM_DOWN |

|

| 50 | 49 |

| R291 |

|

| RD | 9 |

| 2 | VOLUM_UP |

|

| 4.7K |

|

|

| 10 |

| 1 | REPEAT | |||

| PIN GND1~2 =GND |

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| ||

| C350 | C346 |

| C345 | C344 |

|

|

|

|

| +5VCDROM | |

|

|

|

|

|

|

|

|

|

|

| ||

| 10UF/10V | 220UF/6.3V | 0.1UF | 0.1UF |

|

|

| CDMARQ | R259 | 10K(R) |

| |

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

| CDMACK# R277 | 10K |

| |

|

|

|

|

|

|

|

|

| CDIORDY# R270 | 10K |

| |

| +3VS |

| +3VS |

|

|

|

|

|

| +3VCDROM | ||

|

|

|

|

|

|

| F_DD6 | R687 | 10K |

| ||

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

| F_DD7 | R693 | 10K |

|

| R675 |

|

|

|

|

|

|

| SD_DAT2 | R696 | 10K |

|

| 4.7K |

|

| R289 |

|

|

|

| C_ACRST#R658 | 10K |

| |

|

|

|

| 10K(R) |

|

|

|

| CRESET | R728 | 680 |

|

| SDIORDY |

|

| IRQ15 | SDD7 |

|

|

| F_WE | R694 | 10K |

|

|

|

|

|

|

|

|

| |||||

| SDDREQ |

|

|

|

|

|

|

| SD_DAT1 | R707 | 10K |

|

|

|

|

|

|

|

|

|

| C_SDIN0 | R655 | 10K |

|

|

|

|

| R288 |

| R661 |

|

| C_SDOUT R651 | 10K |

| |

| R674 |

|

| 10K |

| 10K(R) |

|

|

|

|

|

|

| 5.6K |

|

|

|

|

|

|

|

|

|

|

|

(12) | IRQ15 | IRQ15 | 103 | H_DASP# | port3[6]/OSC32 |

|

|

|

| 10K |

|

SDDACK# | 117 | H_INTRQ |

| 75 | XTALI245 |

|

|

|

| ||

(12) | SDDACK# | SDIORDY | 122 | H_DMACK# | XTALI245 | 74 | XTAL0245 |

|

|

|

|

(12) | SDIORDY | SDIOR# | 128 | H_DIORDY# | XTALO245 |

|

|

|

|

|

|

(12) | SDIOR# | SDCS#3 |

| H_DIOR# | XTALI48 | 76 |

|

|

| C352 | 18PF |

(12) | SDCS#3 | 91 |

| 77 |

|

|

|

|

| ||

SDCS#1 | 93 | H_CS1 | XTALO48 |

|

|

|

|

|

| ||

(12) | SDCS#1 | SDA2 |

| H_CS0 | USB- | 78 | R702 |

| R300 | Y9 |

|

| SDA[0..2] | 96 |

| 79 |

|

|

|

|

| ||

(12) SDA[0..2] | SDA0 | 98 | H_DA2 | USB+ |

| 10K |

| 5.1M | 48MHz |

| |

| SDA1 | 100 | H_DA0 | TESTO | 37 |

|

|

|

|

| |

|

|

|

| H_DA1 | 46 |

|

|

| C353 | 18PF | |

|

|

|

|

| TEST |

|

|

| |||

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

| USBClkSel 1 | R271 | L58 | 2.7UH | C357 | 1000PF | |

VIN |

|

|

|

| 2.7K(R) |

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| |

VIN | (14,16,24,32,33,34,35) | +3VCDROM |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| |||

VDD5 |

|

|

|

|

|

|

|

|

|

|

|

VDD5 | (13,14,16,18,23,24,26,32) | R671 | R684 | CHECK |

| ||||||

+5VCDROM |

|

| 2.7K | 3.3K |

|

|

|

|

|

|

|

+5VCDROM | (25,26) |

| ADJ_SMCLK | 7 | U28 |

| 6 |

|

| ||

| YA | 1A | H8_SMCLK | (14,24,35) | |||||||

|

|

|

| ADJ_SMDATA | 9 | 5 | |||||

|

|

|

| YB | 2A | SMBCLK | (2,5,12,20) | ||||

|

|

|

|

|

|

| 4 | ||||

|

|

|

|

|

|

|

| 3A |

|

| |

|

| (3,24,32) DD_ON | R670 |

| 0 | 14 |

| 3 |

|

| |

|

|

| S0 | 4A |

|

| |||||

|

|

|

|

| 2 |

|

|

| |||

+3VCDROM |

|

|

|

|

| 1 | S1 |

|

|

|

|

|

|

|

|

| AOE# |

|

|

|

| ||

|

|

| +3VCDROM |

|

| 15 |

| 10 | H8_SMDATA (14,24,35) | ||

|

|

|

|

| BOE# | 1B | |||||

+3VCDROM | (16,26) |

|

|

|

| 11 | |||||

|

|

|

|

| 2B | SMBDATA (2,5,12,20) | |||||

|

|

| 16 |

| 12 | ||||||

|

|

|

|

|

| VCC | 3B |

|

| ||

+3V |

|

|

|

|

|

| 13 |

|

| ||

|

|

|

|

| 8 |

| 4B |

|

| ||

|

|

|

|

|

| GND |

|

|

| ||

|

|

| C909 |

|

|

|

|

|

| ||

+3V | (11,14,17,18,19,20,21,24,29,32,33) |

|

|

|

|

|

|

| |||

0.1UF |

|

|

| QS3253 |

|

|

|

| |||

+3VS |

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| |

+3VCDROM

+5VCDROM

C | D42 |

| R697 |

|

| U575 | 100ms |

| |

|

|

| 30K |

| 1 |

| 4 | ADJ_RESET# | |

ARB751V |

|

| 2 |

| |||||

|

|

|

|

|

| ||||

|

|

| C915 |

|

| 3 | TC7SZ08 |

|

|

|

|

|

|

|

|

|

| ||

|

|

| 10UF(0805) |

|

|

|

|

| |

|

| (24) | H8_ADJRST# | R695 | 33(R) |

| |||

|

|

|

|

|

| ||||

|

|

|

| +3VCDROM |

|

|

| ||

| Use for optional code |

|

| R686 | R685 | C914 | |||

| upgrade |

|

|

|

| R692 | |||

|

|

|

|

|

|

| 0.1UF | ||

| 1 | U32 |

| 8 |

|

| 2.2K(R) | 2.2K | 2.2K |

| A0 | VCC |

| WP |

|

|

| ||

| 2 | 7 |

|

|

|

| |||

| 3 | A1 | WP | 6 |

| LCD_WR |

|

| |

| 4 | NC/A2 SCL | 5 |

| LCD_DATA |

|

| ||

|

| VSS SDA |

|

|

|

|

|

| |

|

| 24LC256P |

|

|

|

|

|

| |

設定在A0的位置

VIN

J4

1 |

|

|

|

| RD | RD | ||

|

|

|

| FF |

| |||

2 |

|

| PLAY_PAUSE | FF | ||||

3 |

|

| STOP_EJECT |

| PLAY_PAUSE | |||

4 |

|

| VOLUM_DOWN |

| STOP_EJECT | |||

5 |

|

| VOLUM_UP | VOLUM_DOWN (24) | ||||

6 |

|

| VOLUM_UP (24) | |||||

|

| REPEAT |

| |||||

7 |

|

| ADJ_PWRS |

| REPEAT | |||

8 |

|

|

|

|

| +3VCDROM | ADJ_PWRS (26,32) | |

9 |

|

|

|

|

|

| ||

10 |

|

|

|

| EL_ON |

|

| |

11 |

|

|

|

|

| |||

|

|

|

| LCD_CS |

|

| ||

12 |

|

|

|

|

| |||

|

|

|

| LCD_WR |

|

| ||

13 |

|

|

|

|

| |||

|

|

|

| LCD_DATA |

| |||

14 |

|

|

|

|

| |||

|

|

|

|

|

|

|

| |

15 |

|

|

|

|

|

|

|

|

16![]()

![]()

17![]()

![]() CIR_RX

CIR_RX

18CIR_RX (16,24,29)

20![]()

![]() VDD5

VDD5

22 |

| VIN | +5VCDROM |

23 |

|

| VIN |

24 | C341 | C923 | C924 |

CON24

0.1U 0.1U 4.7U(0805)

+3VS | VIN | (14,16,24,32,33,34,35) |

(2,8,9,10,11,12,13,14,15,16,19,20,21,22,24,25,29,31,32,33) |

|

B - 28 AUDIO DJ BBVL + CONTROL