2 Fibre Channel is a key technology for storage

Fibre Channel is a serial communications technology designed to transfer large amounts of data among a variety of hardware systems over long distances. It is a key technology for applications that require shared, high bandwidth access to storage.

Fibre Channel provides a logical,

The Fibre Channel architecture is structured as a hierarchical set of protocol layers. Defined within these layers are rules for signal interfaces, serial encoding and decoding, error control, frame format and communications protocols.

ATTO ExpressPCI Fibre Channel host adapters carry SCSI protocol over Fibre Channel.

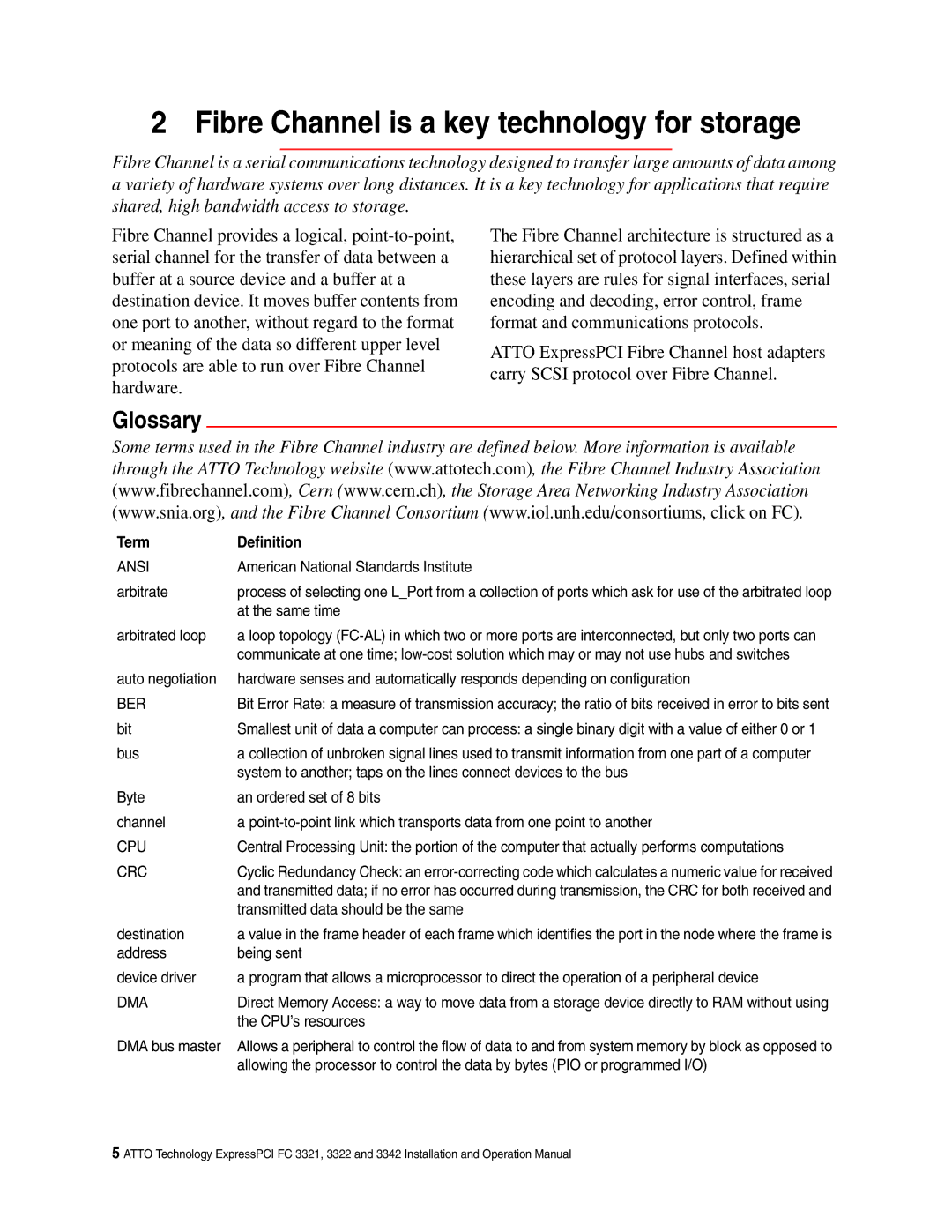

Glossary

Some terms used in the Fibre Channel industry are defined below. More information is available through the ATTO Technology website (www.attotech.com), the Fibre Channel Industry Association (www.fibrechannel.com), Cern (www.cern.ch), the Storage Area Networking Industry Association (www.snia.org), and the Fibre Channel Consortium (www.iol.unh.edu/consortiums, click on FC).

Term | Definition |

ANSI | American National Standards Institute |

arbitrate | process of selecting one L_Port from a collection of ports which ask for use of the arbitrated loop |

| at the same time |

arbitrated loop | a loop topology |

| communicate at one time; |

auto negotiation | hardware senses and automatically responds depending on configuration |

BER | Bit Error Rate: a measure of transmission accuracy; the ratio of bits received in error to bits sent |

bit | Smallest unit of data a computer can process: a single binary digit with a value of either 0 or 1 |

bus | a collection of unbroken signal lines used to transmit information from one part of a computer |

| system to another; taps on the lines connect devices to the bus |

Byte | an ordered set of 8 bits |

channel | a |

CPU | Central Processing Unit: the portion of the computer that actually performs computations |

CRC | Cyclic Redundancy Check: an |

| and transmitted data; if no error has occurred during transmission, the CRC for both received and |

| transmitted data should be the same |

destination | a value in the frame header of each frame which identifies the port in the node where the frame is |

address | being sent |

device driver | a program that allows a microprocessor to direct the operation of a peripheral device |

DMA | Direct Memory Access: a way to move data from a storage device directly to RAM without using |

| the CPU’s resources |

DMA bus master | Allows a peripheral to control the flow of data to and from system memory by block as opposed to |

| allowing the processor to control the data by bytes (PIO or programmed I/O) |

5 ATTO Technology ExpressPCI FC 3321, 3322 and 3342 Installation and Operation Manual