PROTOCOL CONVERTER A/S-2G

4.2 SYNCHRONOUS DEVICE TO ASYNCHRONOUS DEVICE

4.2.1 LINE CONTROL

When the A/S-2G is initially connected to an AC power source or reset, the synchronous device can gain control of the line by sending an ENQ.

When the asynchronous side has control of the line, a turnaround cannot occur until an “End of Transmission” character has been entered from the controlling device. This character will be a “Control D” (ASCII 04 Hex) on the asynchronous side.

4.2.2 SYNCHRONOUS INPUT DATA FORMAT

The synchronous side of the A/S-2G is programmed to receive data whose format is completely specified by the protocol in use (2770, 2780, 3741, or 3780). It will be in EBCDIC code at a data rate of up to 9600 bps.

4.2.3 DATA CONVERSION

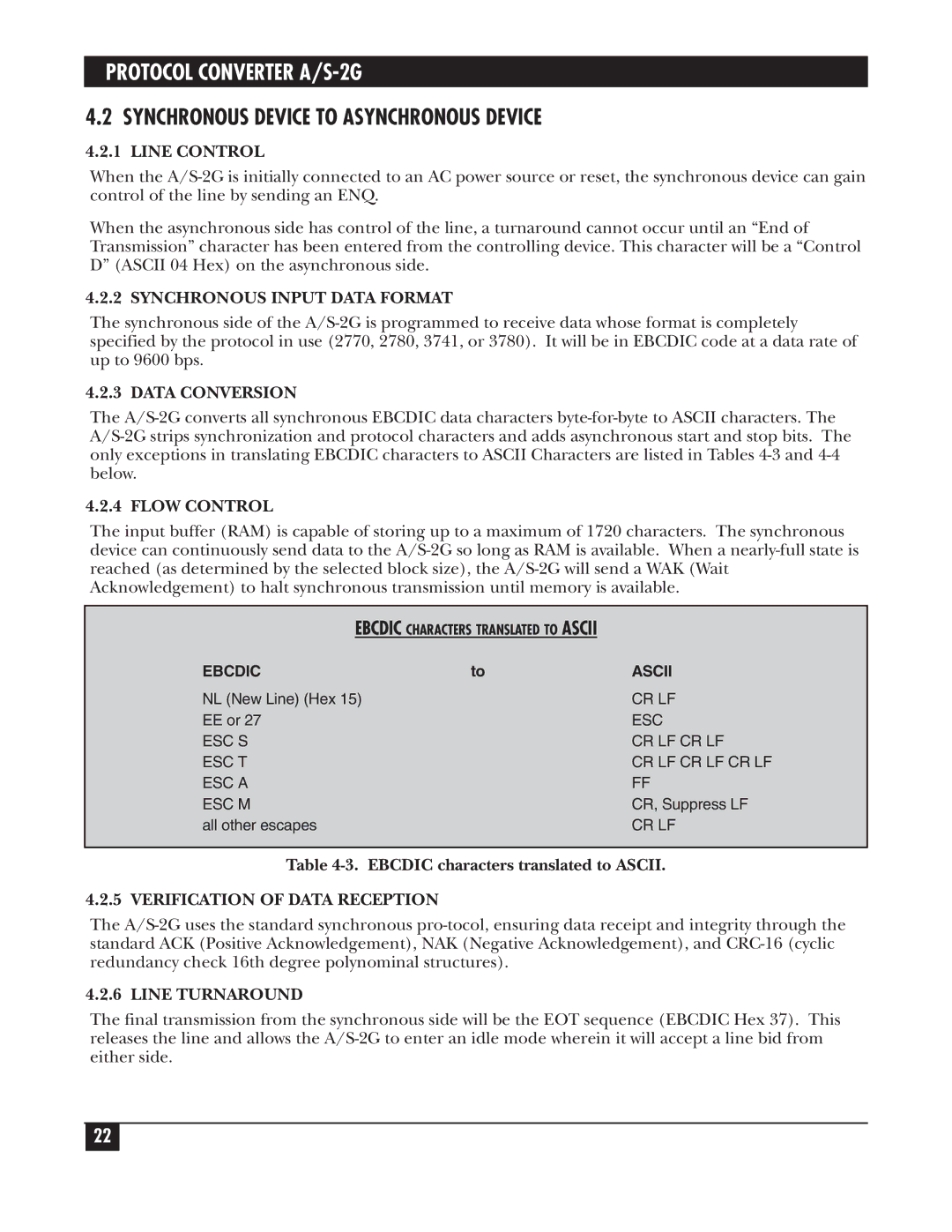

The A/S-2G converts all synchronous EBCDIC data characters byte-for-byte to ASCII characters. The A/S-2G strips synchronization and protocol characters and adds asynchronous start and stop bits. The only exceptions in translating EBCDIC characters to ASCII Characters are listed in Tables 4-3 and 4-4 below.

4.2.4 FLOW CONTROL

The input buffer (RAM) is capable of storing up to a maximum of 1720 characters. The synchronous device can continuously send data to the A/S-2G so long as RAM is available. When a nearly-full state is reached (as determined by the selected block size), the A/S-2G will send a WAK (Wait Acknowledgement) to halt synchronous transmission until memory is available.

| EBCDIC CHARACTERS TRANSLATED TO ASCII | |

EBCDIC | to | ASCII |

NL (New Line) (Hex 15) | CR LF |

EE or 27 | | ESC |

ESC S | | CR LF CR LF |

ESC T | | CR LF CR LF CR LF |

ESC A | | FF |

ESC M | | CR, Suppress LF |

all other escapes | | CR LF |

| | |

Table 4-3. EBCDIC characters translated to ASCII.

4.2.5 VERIFICATION OF DATA RECEPTION

The A/S-2G uses the standard synchronous pro-tocol, ensuring data receipt and integrity through the standard ACK (Positive Acknowledgement), NAK (Negative Acknowledgement), and CRC-16 (cyclic redundancy check 16th degree polynominal structures).

4.2.6 LINE TURNAROUND

The final transmission from the synchronous side will be the EOT sequence (EBCDIC Hex 37). This releases the line and allows the A/S-2G to enter an idle mode wherein it will accept a line bid from either side.