Configuration Examples for EHWIC 1

|

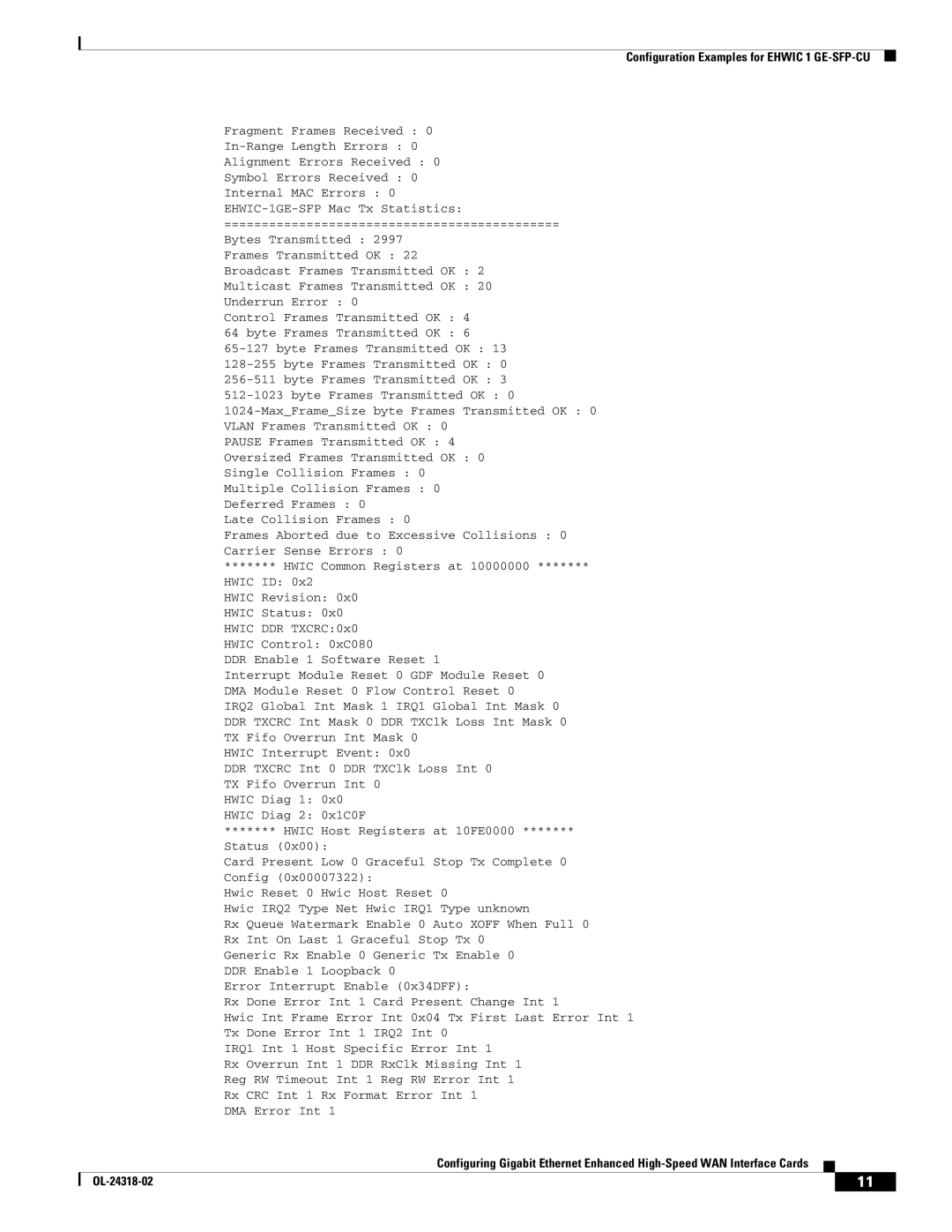

| Fragment Frames Received : 0 | |||

|

| ||||

|

| Alignment Errors Received : 0 | |||

|

| Symbol Errors Received : 0 | |||

|

| Internal MAC Errors : 0 | |||

|

| ||||

|

| ============================================= |

|

|

|

|

| Bytes Transmitted : 2997 | |||

|

| Frames Transmitted OK : 22 | |||

|

| Broadcast Frames Transmitted OK : 2 | |||

|

| Multicast Frames Transmitted OK : 20 | |||

|

| Underrun Error : 0 | |||

|

| Control Frames Transmitted OK : 4 | |||

|

| 64 byte Frames Transmitted OK : 6 | |||

|

| ||||

|

| ||||

|

| ||||

|

| ||||

|

| ||||

|

| VLAN Frames Transmitted OK : 0 | |||

|

| PAUSE Frames Transmitted OK : 4 | |||

|

| Oversized Frames Transmitted OK : 0 | |||

|

| Single Collision Frames : 0 | |||

|

| Multiple Collision Frames : 0 | |||

|

| Deferred Frames : 0 | |||

|

| Late Collision Frames : 0 | |||

|

| Frames Aborted due to Excessive Collisions : 0 | |||

|

| Carrier Sense Errors : 0 | |||

|

| ******* HWIC Common Registers at 10000000 ******* | |||

|

| HWIC ID: 0x2 | |||

|

| HWIC Revision: 0x0 | |||

|

| HWIC Status: 0x0 | |||

|

| HWIC DDR TXCRC:0x0 | |||

|

| HWIC Control: 0xC080 | |||

|

| DDR Enable 1 Software Reset 1 | |||

|

| Interrupt Module Reset 0 GDF Module Reset 0 | |||

|

| DMA Module Reset 0 Flow Control Reset 0 | |||

|

| IRQ2 Global Int Mask 1 IRQ1 Global Int Mask 0 | |||

|

| DDR TXCRC Int Mask 0 DDR TXClk Loss Int Mask 0 | |||

|

| TX Fifo Overrun Int Mask 0 | |||

|

| HWIC Interrupt Event: 0x0 | |||

|

| DDR TXCRC Int 0 DDR TXClk Loss Int 0 | |||

|

| TX Fifo Overrun Int 0 | |||

|

| HWIC Diag 1: 0x0 | |||

|

| HWIC Diag 2: 0x1C0F | |||

|

| ******* HWIC Host Registers at 10FE0000 ******* | |||

|

| Status (0x00): | |||

|

| Card Present Low 0 Graceful Stop Tx Complete 0 | |||

|

| Config (0x00007322): | |||

|

| Hwic Reset 0 Hwic Host Reset 0 | |||

|

| Hwic IRQ2 Type Net Hwic IRQ1 Type unknown | |||

|

| Rx Queue Watermark Enable 0 Auto XOFF When Full 0 | |||

|

| Rx Int On Last 1 Graceful Stop Tx 0 | |||

|

| Generic Rx Enable 0 Generic Tx Enable 0 | |||

|

| DDR Enable 1 Loopback 0 | |||

|

| Error Interrupt Enable (0x34DFF): | |||

|

| Rx Done Error Int 1 Card Present Change Int 1 | |||

|

| Hwic Int Frame Error Int 0x04 Tx First Last Error Int 1 | |||

|

| Tx Done Error Int 1 IRQ2 Int 0 | |||

|

| IRQ1 Int 1 Host Specific Error Int 1 | |||

|

| Rx Overrun Int 1 DDR RxClk Missing Int 1 | |||

|

| Reg RW Timeout Int 1 Reg RW Error Int 1 | |||

|

| Rx CRC Int 1 Rx Format Error Int 1 | |||

|

| DMA Error Int 1 | |||

|

| Configuring Gigabit Ethernet Enhanced |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

| 11 |

| |

|

|

|

| ||