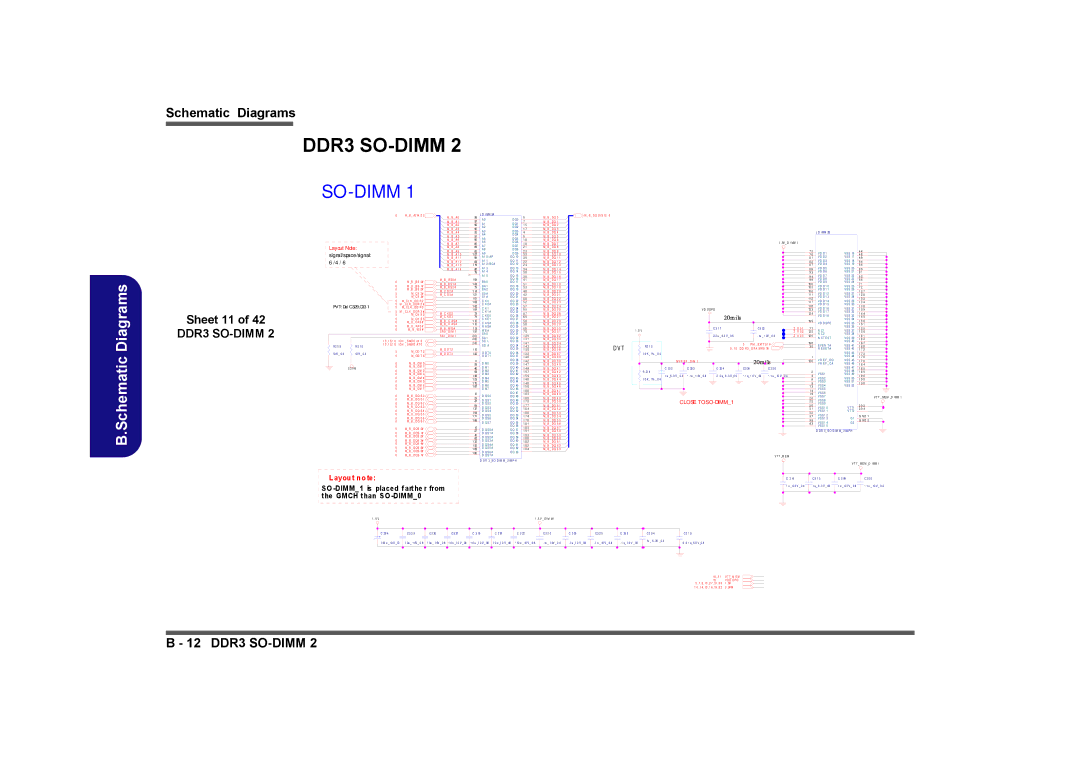

Schematic Diagrams

DDR3 SO-DIMM 2

SO-DIMM 1

B.Schematic Diagrams![]()

Sheet 11 of 42

DDR3 SO-DIMM 2

|

|

| 6 | M_ B _ A [ 14 : 0 ] |

|

|

| M_ B _ A 0 |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| M_ B _ A 1 |

|

|

|

|

|

|

|

| M_ B _ A 2 |

|

|

|

|

|

|

|

| M_ B _ A 3 |

|

|

|

|

|

|

|

| M_ B _ A 4 |

|

|

|

|

|

|

|

| M_ B _ A 5 |

|

|

|

|

|

|

|

| M_ B _ A 6 |

Layout Note: |

|

|

|

|

| M_ B _ A 7 | ||

|

|

|

|

| M_ B _ A 8 | |||

|

|

|

|

| M_ B _ A 9 | |||

signal/space/signal: |

|

|

|

| M_ B _ A 1 0 | |||

|

|

|

| M_ B _ A 1 1 | ||||

6 / 4 / 6 |

|

|

|

|

| M_ B _ A 1 2 | ||

|

|

|

|

| M_ B _ A 1 3 | |||

|

|

|

|

|

|

|

| M_ B _ A 1 4 |

|

|

| 6 | M _B _B S 0# |

| M_ B _ B S 0 # | ||

|

|

|

| M_ B _ B S 1 # | ||||

|

|

| 6 | M _B _B S 1# |

| M_ B _ B S 2 # | ||

|

|

| 6 | M _B _B S 2# |

| M_ C S 2 # | ||

|

|

| 5 | M_ C S 2# |

| M_ C S 3 # | ||

|

|

| 5 | M_ C S 3# |

|

|

| |

|

|

|

|

|

| |||

|

|

| 5 | M_ C L K _ D D R 2 |

|

|

| |

PVT: Del C329,C331 | 5 | M _ C L K _ D D R 2 # |

|

|

| |||

5 | M_ C L K _ D D R 3 |

|

|

| ||||

|

|

| ||||||

|

|

| 5 | M _ C L K _ D D R 3 # |

|

|

| |

|

|

|

| M_ C K E 2 | ||||

|

|

| 5 | M_ C K E 2 |

| |||

|

|

|

| M_ C K E 3 | ||||

|

|

| 5 | M_ C K E 3 |

| |||

|

|

|

| M_ B _ C A S # | ||||

|

|

| 6 | M_ B _ C A S # |

| |||

|

|

| 6 | M_ B _ R A S # |

| M_ B _ R A S # | ||

|

|

|

| M_ B _ W E # | ||||

|

|

| 6 | M_ B _ W E # |

| |||

|

|

|

| S A 0 _ D I M 1 | ||||

|

|

|

|

|

|

| ||

|

|

|

|

|

|

| S A 1 _ D I M 1 | |

|

|

| 1 0 , 1 5, 1 8 I C H _ S MB C LK 0 |

|

|

| ||

|

|

|

|

|

| |||

R 2 0 9 |

| R 2 1 0 | 1 0 , 1 5, 1 8 I C H _ S MB D A T 0 |

| M_ O D T 2 | |||

|

|

|

|

| ||||

|

|

| 5 | M_ OD T 2 |

| |||

10 K _ 0 4 |

| 10 K _ 0 4 |

| M_ O D T 3 | ||||

| 5 | M_ OD T 3 |

| |||||

|

|

|

|

|

| |||

|

|

| 6 | M_ B _ D M 0 |

|

|

| |

|

|

|

|

|

| |||

| 3. 3 V M | 6 | M_ B _ D M 1 |

|

|

| ||

|

|

|

| |||||

|

|

| 6 | M_ B _ D M 2 |

|

|

| |

|

|

| 6 | M_ B _ D M 3 |

|

|

| |

|

|

| 6 | M_ B _ D M 4 |

|

|

| |

|

|

| 6 | M_ B _ D M 5 |

|

|

| |

|

|

|

|

|

| |||

|

|

| 6 | M_ B _ D M 6 |

|

|

| |

|

|

| 6 | M_ B _ D M 7 |

|

|

| |

|

|

| 6 | M_ B _ D Q S 0 |

|

|

| |

|

|

|

|

|

| |||

|

|

| 6 | M_ B _ D Q S 1 |

|

|

| |

|

|

| 6 | M_ B _ D Q S 2 |

|

|

| |

|

|

|

|

|

| |||

|

|

| 6 | M_ B _ D Q S 3 |

|

|

| |

|

|

| 6 | M_ B _ D Q S 4 |

|

|

| |

|

|

| 6 | M_ B _ D Q S 5 |

|

|

| |

|

|

| 6 | M_ B _ D Q S 6 |

|

|

| |

|

|

| 6 | M_ B _ D Q S 7 |

|

|

| |

|

|

| 6 | M_ B _ D QS 0# |

|

|

| |

|

|

| 6 | M_ B _ D QS 1# |

|

|

| |

|

|

| 6 | M_ B _ D QS 2# |

|

|

| |

|

|

|

|

|

| |||

|

|

| 6 | M_ B _ D QS 3# |

|

|

| |

|

|

| 6 | M_ B _ D QS 4# |

|

|

| |

|

|

|

|

|

| |||

|

|

| 6 | M_ B _ D QS 5# |

|

|

| |

|

|

| 6 | M_ B _ D QS 6# |

|

|

| |

|

|

| 6 | M_ B _ D QS 7# |

|

|

| |

|

|

|

|

|

| |||

98

97

96

95

92

91

90

86

89

85

107

84

83

119

80

78

109

108

79

114

121

101

103

102

104

73

74

115

110

113

197

201

202

2 00

116

120

11

28

46

63

136

153

170

187

12

29

47

64

137

154

171

188

10

27

45

62

135

152

169

186

J D | I MM 2A |

| ||

A 0 |

|

| D Q0 | |

A 1 |

|

| D Q1 | |

A 2 |

|

| D Q2 | |

A 3 |

|

| D Q3 | |

A 4 |

|

| D Q4 | |

A 5 |

|

| D Q5 | |

A 6 |

|

| D Q6 | |

A 7 |

|

| D Q7 | |

A 8 |

|

| D Q8 | |

A 9 |

|

| D Q9 | |

A 1 0 / A P | D Q 10 | |||

A 1 1 |

|

| D Q 11 | |

A 1 2 / B C # | D Q 12 | |||

A 1 3 |

|

| D Q 13 | |

A 1 4 |

|

| D Q 14 | |

A 1 5 |

|

| D Q 15 | |

B A 0 |

|

| D Q 16 | |

|

| D Q 17 | ||

B A 1 |

|

| D Q 18 | |

B A 2 |

|

| D Q 19 | |

S 0 # |

|

| D Q 20 | |

S 1 # |

|

| D Q 21 | |

C K 0 | # |

| D Q 22 | |

C K 0 |

| D Q 23 | ||

C K 1 | # |

| D Q 24 | |

C K 1 |

| D Q 25 | ||

C K E | 0 |

| D Q 26 | |

C K E | 1 |

| D Q 27 | |

C A S | # |

| D Q 28 | |

R A S # |

| D Q 29 | ||

W E # |

|

| D Q 30 | |

S A 0 |

|

| D Q 31 | |

S A 1 |

|

| D Q 32 | |

S C L |

|

| D Q 33 | |

S D A |

|

| D Q 34 | |

|

|

|

| D Q 35 |

O D T 0 |

| D Q 36 | ||

O D T 1 |

| D Q 37 | ||

D | M0 |

|

| D Q 38 |

|

| D Q 39 | ||

D | M1 |

|

| D Q 40 |

D | M2 |

|

| D Q 41 |

D | M3 |

|

| D Q 42 |

D | M4 |

|

| D Q 43 |

D | M5 |

|

| D Q 44 |

D | M6 |

|

| D Q 45 |

D | M7 |

|

| D Q 46 |

D QS | 0 |

| D Q 47 | |

| D Q 48 | |||

D QS | 1 |

| D Q 49 | |

D QS | 2 |

| D Q 50 | |

D QS | 3 |

| D Q 51 | |

D QS | 4 |

| D Q 52 | |

D QS | 5 |

| D Q 53 | |

D QS | 6 |

| D Q 54 | |

D QS | 7 |

| D Q 55 | |

|

|

|

| D Q 56 |

D QS | 0 | # | D Q 57 | |

D QS | 1 | # | D Q 58 | |

D QS | 2 | # | D Q 59 | |

D QS | 3 | # | D Q 60 | |

D QS | 4 | # | D Q 61 | |

D QS | 5 | # | D Q 62 | |

D QS | 6 | # | D Q 63 | |

D QS | 7 | # |

| |

D D R 3 _S O D I M M_ 2 04 P H

5

7

15

17

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

1 2 9

1 3 1

1 4 1

1 4 3

1 3 0

1 3 2

1 4 0

1 4 2

1 4 7

1 4 9

1 5 7

1 5 9

1 4 6

1 4 8

1 5 8

1 6 0

1 6 3

1 6 5

1 7 5

1 7 7

1 6 4

1 6 6

1 7 4

1 7 6

1 8 1

1 8 3

1 9 1

1 9 3

1 8 0

1 8 2

1 9 2

1 9 4

M_ B _ D Q 0

M_ B _ D Q 1 M_ B _ D Q 2

M_ B _ D Q 3 M_ B _ D Q 4

M_ B _ D Q 5 M_ B _ D Q 6

M_ B _ D Q 7 M_ B _ D Q 8

M_ B _ D Q 9 M_ B _ D Q 1 0 M_ B _ D Q 1 1

M_ B _ D Q 1 2 M_ B _ D Q 1 3

M_ B _ D Q 1 4 M_ B _ D Q 1 5

M_ B _ D Q 1 6 M_ B _ D Q 1 7

M_ B _ D Q 1 8 M_ B _ D Q 1 9

M_ B _ D Q 2 0 M_ B _ D Q 2 1

M_ B _ D Q 2 2 M_ B _ D Q 2 3

M_ B _ D Q 2 4 M_ B _ D Q 2 5

M_ B _ D Q 2 6 M_ B _ D Q 2 7

M_ B _ D Q 2 8 M_ B _ D Q 2 9

M_ B _ D Q 3 0 M_ B _ D Q 3 1

M_ B _ D Q 3 2 M_ B _ D Q 3 3

M_ B _ D Q 3 4 M_ B _ D Q 3 5 M_ B _ D Q 3 6

M_ B _ D Q 3 7 M_ B _ D Q 3 8

M_ B _ D Q 3 9 M_ B _ D Q 4 0

M_ B _ D Q 4 1 M_ B _ D Q 4 2

M_ B _ D Q 4 3 M_ B _ D Q 4 4

M_ B _ D Q 4 5 M_ B _ D Q 4 6

M_ B _ D Q 4 7 M_ B _ D Q 4 8

M_ B _ D Q 4 9 M_ B _ D Q 5 0

M_ B _ D Q 5 1 M_ B _ D Q 5 2

M_ B _ D Q 5 3 M_ B _ D Q 5 4

M_ B _ D Q 5 5 M_ B _ D Q 5 6

M_ B _ D Q 5 7 M_ B _ D Q 5 8

M_ B _ D Q 5 9 M_ B _ D Q 6 0 M_ B _ D Q 6 1

M_ B _ D Q 6 2 M_ B _ D Q 6 3

![]() M_ B _ D Q [ 6 3: 0] 6

M_ B _ D Q [ 6 3: 0] 6

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| J D I MM 2B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 . 5V _ D I MM 1 |

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 7 5 | V D D 1 | V S S 16 | 4 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 7 6 | 4 8 |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 8 1 | V D D 2 | V S S 17 | 4 9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 8 2 | V D D 3 | V S S 18 | 5 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 8 7 | V D D 4 | V S S 19 | 5 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 8 8 | V D D 5 | V S S 20 | 6 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 9 3 | V D D 6 | V S S 21 | 6 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 9 4 | V D D 7 | V S S 22 | 6 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 9 9 | V D D 8 | V S S 23 | 6 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 10 0 | V D D 9 | V S S 24 | 7 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 10 5 | V D D 1 0 | V S S 25 | 7 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 10 6 | V D D 1 1 | V S S 26 | 1 2 7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 11 1 | V D D 1 2 | V S S 27 | 1 2 8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 11 2 | V D D 1 3 | V S S 28 | 1 3 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 11 7 | V D D 1 4 | V S S 29 | 1 3 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 11 8 | V D D 1 5 | V S S 30 | 1 3 8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| V D D S P D |

|

|

|

|

|

|

|

|

|

|

|

| 12 3 | V D D 1 6 | V S S 31 | 1 3 9 |

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 12 4 | V D D 1 7 | V S S 32 | 1 4 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 20m ils |

|

|

|

|

|

|

|

|

|

|

|

|

| V D D 1 8 | V S S 33 | 1 4 5 |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 19 9 | V D D S P D | V S S 34 | 1 5 0 |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| V S S 35 | 1 5 1 |

|

|

|

|

|

|

| |

| 1 . 5 V |

|

| C 3 1 7 |

|

|

| C 3 23 |

|

| Z 11 0 1 | 7 7 | N C 1 | V S S 36 | 1 5 5 |

|

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z 11 0 2 | 12 2 | V S S 37 | 1 5 6 |

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

| 2. 2 u _ 6. 3 V _ 0 6 |

|

|

| . 1u _ 1 0V _ 0 4 |

| Z 11 0 3 | 12 5 | N C 2 | V S S 38 | 1 6 1 |

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| N C T E S T | V S S 39 | 1 6 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| V S S 40 |

|

|

|

|

|

|

|

|

D V T |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 5 | P M _ E XT T S 1 # |

|

| 19 8 | E V E N T # | V S S 41 | 1 6 7 |

|

|

|

|

|

|

| ||||||||

| R 2 1 5 |

|

|

|

|

|

|

| 3 0 | 1 6 8 |

|

|

|

|

|

|

| ||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

| 5 , 1 0 D D R 3 _ D R A MR S T# |

|

|

| R E S E T # | V S S 42 | 1 7 2 |

|

|

|

|

|

|

| |||||||||||||

|

| 1 0 K _ 1% _ 0 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| V S S 43 | 1 7 3 |

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 | V R E F _ D Q | V S S 44 | 1 7 8 |

|

|

|

|

|

|

|

|

|

|

|

| MV R E F _ D I M 1 |

|

|

|

|

| 20m |

| ils |

| 12 6 | V S S 45 | 1 7 9 |

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| V R E F _ C A | V S S 46 | 1 8 4 |

|

|

|

|

|

|

| ||||||||

|

|

|

|

| C 33 2 |

| C 33 3 | C 32 4 | C 3 34 |

|

|

|

|

|

|

|

| C 3 2 6 |

|

|

| V S S 47 | 1 8 5 |

|

|

|

|

|

|

| |||||||

|

| R 21 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2 | V S S 1 | V S S 48 | 1 8 9 |

|

|

|

|

|

|

| ||

|

|

|

|

| 1 u _6 . 3 V _ 0 4 | * . 1u _ 1 0V _ 0 4 | 2 . 2 u_ 6 . 3 V _0 6 | *. 1 u_ 1 0 V _ 04 | *. 1 u _ 10 V _ | 0 4 |

| 3 | V S S 49 | 1 9 0 |

|

|

|

|

|

|

| ||||||||||||||||

|

| 1 0 K _ 1% _ 0 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 8 | V S S 2 | V S S 50 | 1 9 5 |

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 9 | V S S 3 | V S S 51 | 1 9 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 3 | V S S 4 | V S S 52 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 4 | V S S 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 9 | V S S 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CLOSE TO |

|

|

|

|

|

|

|

|

|

|

|

| 2 0 | V S S 7 |

|

| V T T _ ME M _D I MM 1 | ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| V S S 8 |

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2 5 |

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| V S S 9 |

| 2 0 3 |

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2 6 |

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3 1 | V S S 1 0 | V T T1 | 2 0 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3 2 | V S S 1 1 | V T T2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3 7 | V S S 1 2 |

| G N D 1 | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| V S S 1 3 | G1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3 8 | G N D 2 |

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 4 3 | V S S 1 4 | G2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| V S S 1 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| D D R 3_ S O D I M M_ 2 04 P H |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| V T T _M E M |

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| V T T _ ME M _D I MM 1 | ||||||||

L ayou t n o te:

SO -DIMM_1 is placed farthe r from the GMCH than SO -DIMM _0

1 . 5 V | 1 . 5 V _ D I M M1 |

|

|

|

|

|

|

|

|

|

|

|

| C 3 14 |

|

| C 3 1 3 |

|

| C 2 99 |

|

| C 3 0 0 |

| 1 u _ 6. 3 V _ 0 4 |

|

| 1 u_ 6 . 3 V _ 04 |

|

| 1 u _ 6. 3 V _ 0 4 |

|

| *. 1 u _ 10 V _ 0 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C 28 4

+

1 00 u _ 10 V _ D

|

| C 3 3 9 |

|

| C 3 38 |

|

|

| C 3 37 |

|

| C 3 18 |

|

| C 2 81 |

|

| C 3 22 | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 0u _ 1 0V _ 0 8 |

| 1 0u _ 1 0V _ 0 8 |

| 1 0 u _1 0 V _ 08 |

| 1 0 u _1 0 V _ 08 |

| 1 0 u _1 0 V _ 08 |

| * 10 u _ 10 V _ 0 8 | |||||||||||

|

|

|

|

|

| |||||||||||||||||

C 3 2 0

. 1u _ 1 0V _ 0 4

C 3 36

. 1 u _1 0 V _ 04

C 3 2 5

. 1 u _ 10 V _ 0 4

C 33 | 5 |

|

| C 3 0 4 |

. 1 u_ | 1 0 V _ 04 |

|

| 1u _ 6 . 3V _0 4 |

|

|

|

C 3 1 9

0 . 0 1 u_ 5 0 V _0 4

| 10 , 3 1 | V T T_ M E M |

5 , 7 , 9, | 10 | V D D S P D |

10 , 2 7 , 31 , 3 3 | 1 . 5V | |

1 0 , 1 4, | 15 , 1 6 , 18 , 3 2 | 3 . 3V M |

B - 12 DDR3