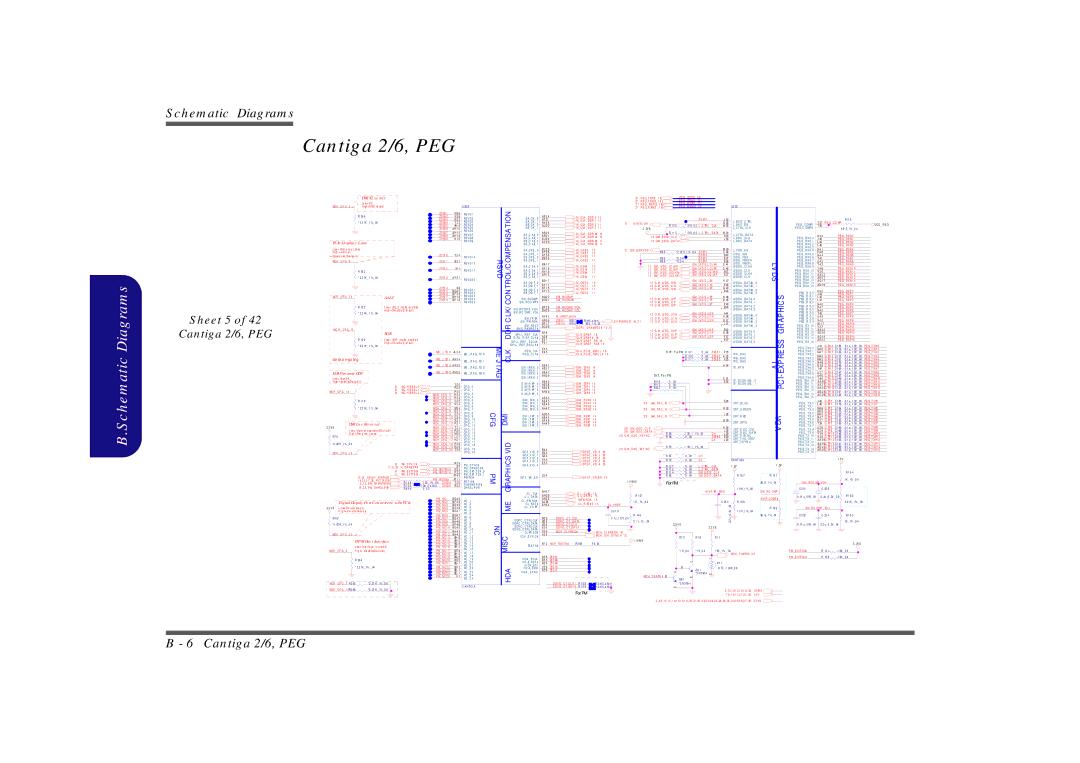

Schematic Diagrams

Cantiga 2/6, PEG

B.Schematic Diagrams![]()

Sheet 5 of 42

Cantiga 2/6, PEG

DMI X2 se lect

| MCH _CF G _5 |

|

|

| Lo w= X 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| U 25 B |

| |

|

|

|

| Hi gh =X 4(D ef au t)l |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z 0 50 1 | M3 6 | RS V D1 |

| |

|

|

|

| R 36 6 |

|

|

|

|

|

|

|

|

|

|

|

|

| Z 0 50 2 | N3 6 |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z 0 50 3 | R3 3 | RS V D2 |

| |

|

|

|

| * 2. 2 1K _ 1 %_ 04 |

|

|

|

|

|

|

|

|

|

|

|

| Z 0 50 4 | T 3 3 | RS V D3 |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z 0 50 5 | AH 9 | RS V D4 |

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z 0 50 6 | A H1 0 | RS V D5 |

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z 0 50 7 | A H1 2 | RS V D6 |

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z 0 50 8 | A H1 3 | RS V D7 |

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z 0 50 9 | K 1 2 | RS V D8 |

| |

| PCIe Graphics Lane |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RS V D9 |

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

| L ow= Rev e rs e L an es |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| Hi gh = Norm a l |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z 0 51 0 | T 2 4 |

|

| |

| Op era ti on (De fau l t) |

|

|

|

|

|

|

|

|

|

|

|

|

| RS V D1 | 4 | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

| MCH _CF G _9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z 0 51 1 | B 3 1 | RS V D1 | 5 | |

|

|

|

| R 36 2 |

|

|

|

|

|

|

|

|

|

|

|

|

| Z 0 51 2 | M 1 | RS V D1 | 7 | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z 0 51 3 | A Y 2 1 | |||||

|

|

|

| * 2. 2 1K _ 1 %_ 04 |

|

|

|

|

|

|

|

|

|

|

|

| RS V D2 | 0 | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z 0 51 4 | B 2 | RS V D2 | 1 | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z 0 51 5 | B G2 3 | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z 0 51 6 | B F 2 3 | RS V D2 2 | ||

| MCH _CF G _1 2 | ALLZ |

|

|

|

|

|

|

|

|

|

|

| Z 0 51 7 | B H1 8 | RS V D2 | 3 | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z 0 51 8 | B F 1 8 | RS V D2 | 4 | |||

|

|

|

| R 12 2 | L ow= | A LL Z | mo de | en a bl ed |

|

|

|

|

|

|

|

|

| RS V D2 | 5 | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

| Hi gh = Dis a bl e (D ef | au t)l |

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

| * 2. 2 1K _ 1 %_ 04 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MC H _ CF G_ 13 | XOR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

| R 12 9 | L ow= | XOR | mo de | e na bl e d |

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

| Hi gh = Dis a bl e (D ef | au t)l |

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

| * 2. 2 1K _ 1 %_ 04 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ME _ J_ TC K | AL 3 4 | ME _ JT A G_ TC K | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

| clo ck u |

|

|

|

|

|

|

|

|

|

|

|

| ME _ J_ TD I | A K 3 4 | ME _ JT A G_ TD I | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ME _ J_ TD O A N3 5 | ME _ JT A G_ TD O | ||||

| FSB Dynamic ODT |

|

|

|

|

|

|

|

|

|

|

|

| ME _ J_ TM S | A M3 5 | ME _ JT A G_ TM S | |||||||

| L ow= di sa b el |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Hi gh = en ab l e(De fa ul t) |

|

|

|

|

|

|

|

|

|

|

|

|

|

| T 2 5 |

|

| |||||

|

|

|

|

|

|

| 18 | MC H _B S E L 0 |

|

|

|

|

|

|

| CF G_ 0 |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| R2 5 |

| ||||||||

|

|

|

|

|

|

| 18 | MC H _B S E L 1 |

|

|

|

|

|

|

|

|

| CF G_ 1 |

| ||||

| MC H _ C F G_ 1 6 |

|

|

|

|

|

|

|

|

|

|

|

| P 2 5 |

| ||||||||

|

|

|

|

|

| 18 | MC H _B S E L 2 |

|

|

|

|

|

|

| CF G_ 2 |

| |||||||

|

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 3 | P 2 0 |

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 4 | P 2 4 | CF G_ 3 |

| |||

|

|

|

| R 11 0 |

|

|

|

|

|

|

|

|

|

|

| MC H _ C F G_ 5 | C2 5 | CF G_ 4 |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 6 | N2 | 4 | CF G_ 5 |

| ||

|

|

|

| * 2. 2 1K _ 1 %_ 04 |

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 7 | M2 | 4 | CF G_ 6 |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| CF G_ 7 |

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 8 | E 2 1 |

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 9 | C2 | 3 | CF G_ 8 |

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 1 0 | C2 | 4 | CF G_ 9 |

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 1 1 | N2 | 1 | CF G_ 1 | 0 | ||

|

| DMI Lne Reversal |

|

|

|

|

|

|

|

|

|

|

|

| CF G_ 1 | 1 | |||||||

|

|

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 1 2 | P 2 1 | ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CF G_ 1 | 2 | |||||

3. 3 V S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 1 3 | T 2 1 | CF G_ 1 | 3 | ||||

|

| L ow= Norm al | o pe rati o n(De fa ul t) |

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 1 4 | R2 0 | ||||||||

|

| Hi gh = Rev e rse L an es |

|

|

|

|

|

|

|

|

|

|

|

| CF G_ 1 | 4 | |||||||

|

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 1 5 | M2 0 | |||||||||||

| R7 9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CF G_ 1 | 5 | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 1 6 | L 2 1 | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CF G_ 1 | 6 | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 1 7 | H2 1 | |||||

| *4 . 02 K _1 % _0 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CF G_ 1 | 7 | ||||

|

|

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 1 8 | P 2 9 | ||||||||||

|

|

|

|

|

|

|

|

|

|

|

| CF G_ 1 | 8 | ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 1 9 | R2 8 | |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CF G_ 1 | 9 | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MCH _ CF G_ 2 0 | T 2 8 | |||||

| MCH _CF G _1 9 |

| 15 | PM _S Y N C# |

|

|

|

|

|

|

| R2 9 | CF G_ 2 | 0 | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| P M_ S Y NC# | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| B 7 | |||||||||

|

|

|

|

|

| 2 , 13 , 35 H _ D P R S T P # |

|

|

|

|

|

|

| P M_ DP RS T P # | |||||||||

|

|

|

|

|

|

|

|

|

| P M_ EX T TS 0 # | N3 3 | ||||||||||||

|

|

|

|

|

|

| 10 | PM _E X TT S 0# |

|

|

|

| P M_ EX T TS 1 # | P 3 2 | P M_ E XT _T S # _0 | ||||||||

|

| 15 ,35 | DE LA Y _P W RGD | 11 | PM _E X TT S 1# |

|

|

|

|

|

|

| AT 4 0 | P M_ E XT _T S # _1 | |||||||||

|

|

|

|

|

|

|

|

|

|

|

| P M_ R S TI N # | AT 1 1 | P W ROK | |||||||||

|

|

|

| 1 4,2 2,3 7 ,38 P LT _R S T# |

|

|

|

|

|

|

|

|

|

| RS T IN# | ||||||||

|

|

|

|

| R1 4 | 8 |

|

|

| 1 00 _ 1% _0 4 | Z 0 53 4 | T 2 0 | |||||||||||

|

| 2 ,1 3 | P M_ TH RMT RIP # |

|

|

|

| T HE RMT RIP # | |||||||||||||||

|

|

| R1 2 6 |

| *1 0m i l s ho rt | Z 0 53 5 | R3 2 | ||||||||||||||||

|

|

|

|

|

|

|

|

| |||||||||||||||

|

| 15 ,3 5 | P M_ DP RS L P VR |

| R3 5 | 9 |

|

| 0 _ | 0 4 |

|

|

|

|

|

| DP RS L P V R | ||||||

| Digital Dispaly Port Concurrent wiht PCie |

|

|

|

|

| P M_ NC1 | B G4 8 | NC _1 |

| |||||||||||||

|

|

|

|

|

| P M_ NC2 | B F 4 8 |

| |||||||||||||||

|

|

|

|

|

| P M_ NC3 | B D4 8 | NC _2 |

| ||||||||||||||

3. 3 V S L o w= On l y(D efa u t)l |

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC4 | B C4 8 | NC _3 |

| |||||||

| H gi h= s mi | ul ta ne ou s yl |

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC5 | B H4 7 | NC _4 |

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| NC _5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC6 | B G4 7 |

| |||

| R3 67 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| NC _6 |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC7 | B E 4 7 |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC8 | B H4 6 | NC _7 |

| ||

| *4 . 02 K _1 % _0 4 |

|

|

|

|

|

|

|

|

|

|

|

| P M_ N C 9 | B F 4 6 | NC _8 |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC1 0 | B G4 5 | NC _9 |

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC1 1 | B H4 4 | NC _1 0 |

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| NC _1 1 |

| ||||

| MCH _CF G _2 0 |

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC1 2 | B H4 3 |

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC1 3 | BH 6 | NC _1 2 |

| ||

|

|

| ITPM Hos t Interface |

|

|

|

|

|

|

|

|

|

|

| P M_ NC1 4 | BH 5 | NC _1 3 |

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC1 5 | BG 4 | NC _1 4 |

| ||||||

|

|

| L ow= In te rfa ce i s e na b el |

|

|

|

|

|

|

|

|

|

|

| P M_ NC1 6 | BH 3 | NC _1 5 |

| |||||

| MCH _ CF G_ 6 |

| H gi h= di s ab l e(De fa ul t) |

|

|

|

|

|

|

|

|

|

|

| P M_ NC1 7 | B F 3 | NC _1 6 |

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

| NC _1 7 |

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC1 8 | BH 2 |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC1 9 | BG 2 | NC _1 8 |

| ||

|

|

| R 36 4 |

|

|

|

|

|

|

|

|

|

|

|

| P M_ N C 2 0 | B E 2 | NC _1 9 |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC2 1 | BG 1 | NC _2 0 |

| ||

|

|

| * 2. 2 1K _ 1% _ 04 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| NC _2 1 |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC2 2 | B F 1 |

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| NC _2 2 |

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC2 3 | BD 1 |

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC2 4 | BC 1 | NC _2 3 |

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P M_ NC2 5 | F 1 | NC _2 4 |

| ||

| MCH _ CF G_ 7 R3 63 | *2 . 21 K _ 1% _0 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| NC _2 5 |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C A NTIG A | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| MC H _ C F G_ 1 0R3 65 | *2 . 21 K _ 1% _0 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RSVD | TROL/C OMPENSA TION |

|

| CON |

|

| C LK/ |

|

| DDR |

| ME J | CLK |

| TAG |

|

CFG |

| DMI |

|

| VID |

PM |

| GRAPH ICS |

|

| ME |

NC | MISC | |

|

| |

|

| HDA |

S A_ CK _ 0

S A_ CK _ 1

S B_ CK _ 0

S B_ CK _ 1

S A _C K #_ 0

S A _C K #_ 1

S B _C K #_ 0

S B _C K #_ 1

S A _CK E _ 0

S A _CK E _ 1

S B _CK E _ 0

S B _CK E _ 1

S A _C S #_ 0

S A _C S #_ 1

S B _C S #_ 0

S B _C S #_ 1

S A _OD T_ 0

S A _OD T_ 1

S B _OD T_ 0

S B _OD T_ 1

S M_ RCOMP

S M_ RCO MP #

S M_ RCOM P_ V OH S M _RC OMP _ V OL

S M_V R EF S M _P W ROK

S M_ RE X T S M_D RA MRS T #

DP L L_ RE F _ CLK

DP LL _R E F_ CL K #

DP L L _RE F _ S S CLK DP LL _ RE F _S S CL K #

P E G_ CLK

P E G_ CL K #

DM I _RX N _ 0

DM I _RX N _ 1

DM I _RX N _ 2

DM I _RX N _ 3

DMI _R XP _ 0 D MI _R XP _ 1 D MI _R XP _ 2

D MI _R XP _ 3

DMI _ TX N _ 0

DMI _ TX N _ 1

DMI _ TX N _ 2

DMI _ TX N _ 3

DM I _T XP _ 0

DM I _T XP _ 1

DM I _T XP _ 2

DM I _T XP _ 3

GF X _V ID _ 0

GF X _V ID _ 1

GF X _V ID _ 2

GF X _V ID _ 3

GF X _V ID _ 4

GF X _ VR _E N

CL _ CLK

C L_ DA TA

CL _P W ROK

CL_ RS T #

CL _V R EF

DDP C _ CT RL CLK DDP C _ CT RL DA TA S DV O_ CT RL CLK S DV O_ CT RL DA TA CL KR E Q#

ICH _S Y N C#

TS A T N#

HDA _ B CLK

HD A_ RS T #

H DA _S DI

HD A_ S DO

HDA _ S Y NC

|

|

|

|

| 37 | P E G_T X P [0 .. 1 5] |

|

|

| P E G_ TX P [0.. 1 5] |

|

|

| ||||

|

|

|

|

| 37 | P E G_T X N[0.. 1 5 ] |

|

|

| P E G_ TX N[0 .. 15 ] |

|

|

| ||||

|

|

|

|

| 3 7 | P E G_ RX P [0.. 1 5] |

|

|

| P E G_ RX P[0 .. 15 ] |

|

|

| ||||

|

|

|

|

| 37 | P E G_R XN[0 .. 1 5] |

|

|

| P E G_ R X N [ 0. . 1 5] |

|

| U2 5C | ||||

A P 2 4 |

| M_ CLK _ DDR 0 | 1 0 |

|

|

|

|

|

|

|

|

|

| Z 0 57 2 |

|

| |

A T 21 |

|

|

|

|

|

|

|

|

|

|

| L 32 |

| ||||

A V 2 4 |

| M_ CLK _ DDR 1 | 1 0 | 12 | G M_B L ON |

|

|

|

|

|

|

|

|

| G 32 | L_ B K LT _C TRL | |

| M_ C LK _ D D R 2 | 1 1 |

|

|

|

|

|

|

|

|

| L_ B K LT _E N | |||||

A U2 0 |

|

| R 12 0 |

| * 10 K _0 4 L _C TRL _ CLK | M 32 | |||||||||||

|

| M_ CLK _ DDR 3 | 1 1 |

|

| 3 . 3V S |

|

|

|

|

|

|

|

|

| L_ CT RL_ CL K | |

A R2 4 |

|

| M_ CLK _ DDR 0# | 10 |

|

|

|

| R 11 5 | * 10 K _0 4 | L _C TRL _ DA TA | M 33 | L_ CT RL_ DA T A |

| |||

A R2 1 |

|

|

|

| 1 2 | GM _E DID _ CL K |

|

|

| K 33 |

| ||||||

|

| M_ CLK _ DDR 1# | 10 |

|

|

|

|

| L_ DDC _CL K |

| |||||||

A U2 4 |

|

| M_ CLK _ DDR 2# | 11 |

|

| 1 2 | GM _E DID _ DA T A |

|

|

| J 33 |

| ||||

A V 2 0 |

|

|

|

|

|

|

|

| L_ DDC _DA T A |

| |||||||

|

|

| M_ CLK _ DDR 3# | 11 |

|

|

|

|

|

|

|

|

|

|

| ||

B C2 8 |

|

| M_ CK E 0 | 1 0 |

|

| 12 GM _E NA V DD | R 8 2 | *2 . 37 K _1 % _0 4 Z 0 57 3 |

| M 29 | L_ V DD _ E N |

| ||||

A Y 2 8 |

|

| M_ C K E 1 | 1 0 |

|

|

|

|

|

| C 44 | LV DS _ IB G |

| ||||

A Y 3 6 |

|

|

|

|

|

|

|

|

|

| Z 0 57 4 |

| B 43 |

| |||

|

| M_ CK E 2 | 1 1 |

|

|

|

|

| R9 3 | *0 _0 4 |

|

| LV DS _ V B G |

| |||

B B 3 6 |

|

| M_ CK E 3 | 1 1 |

|

|

|

|

|

| Z 0 57 5 |

| E 37 |

| |||

B A 1 7 |

|

|

|

|

|

|

| R9 8 | *0 _0 4 |

| Z 0 57 6 |

| E 38 | LV DS _ V RE F H | LV | ||

|

| M_ C S 1# | 1 0 |

|

|

|

| 1 2 | GM_ LV DS _ LC LK P | GM_ LV D S _L CL KN | C 41 | LV DS _ V RE F L | |||||

A Y 1 6 |

|

|

|

|

|

| GM_ LV D S _L CL KP | C 40 | LV DS A _ CL K | ||||||||

|

|

| M_ CS 0# | 1 0 |

|

|

|

| 1 2 | GM_ LV DS _ LC LK N |

|

|

|

| LV DS A _ CL K # |

| |

A V 1 6 |

|

| M_ CS 2# | 1 1 |

|

|

|

| 1 2 | GM_ LV DS _ UCL K N | GM_ LV D S _UC LK N | B 37 | LV DS B _ CL K # | DS | |||

A R1 3 |

|

|

|

|

|

|

|

| 1 2 | GM_ LV DS _ UCL K P | GM_ LV D S _UC LK P | A 37 | |||||

|

|

| M_ CS 3# | 1 1 |

|

|

|

|

|

|

|

| LV DS B _ CL K | ||||

B D1 7 |

|

| M_ ODT 0 | 1 0 |

|

|

|

| 1 2 | G M_ LV DS _ L0 N | GM_ LV D S _L 0N | H 47 | LV DS A _ DA T A# _ 0 |

| |||

A Y 1 7 |

|

| M_ ODT 1 | 1 0 |

|

|

|

| 1 2 | G M_ LV DS _ L1 N | GM_ LV D S _L 1N | E 46 | LV DS A _ DA T A# _ 1 |

| |||

B F 1 5 |

|

| M_ ODT 2 | 1 1 |

|

|

|

| 1 2 | G M_ LV DS _ L2 N | GM_ LV D S _L 2N | G 40 | LV DS A _ DA T A# _ 2 |

| |||

A Y 1 3 |

|

| M_ ODT 3 | 1 1 |

|

|

|

|

|

|

|

|

|

| A 40 |

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| LV DS A _ DA T A# _ 3 | S | ||

B G2 2 | S M_ RCOM P |

|

|

|

|

|

| 1 2 | G M_ LV DS _ L0 P | GM_ LV D S _L 0P | H 48 | LV DS A _ DA T A_ 0 | |||||

B H2 1 | S M_ RCOM P# |

|

|

|

|

|

| GM_ LV D S _L 1P | D 45 | HIC | |||||||

B H2 8 | S M_ RCOM P_ V OL |

|

|

|

|

| 1 2 G M_ LV DS _ L1 P |

|

|

|

| LV DS A _ DA T A_ 3 | |||||

B F 2 8 | S M_ RCOM P_ V OH |

|

|

|

|

| 1 2 | G M_ LV DS _ L2 P | GM_ LV D S _L 2P | F 40 | LV DS A _ DA T A_ 2 |

| |||||

|

|

|

|

|

|

|

|

|

|

| B 40 |

| |||||

| M_ V R E F _M C H |

|

|

|

|

|

| 1 2 | G M_ LV DS _ U0 N | GM_ LV D S _U0 N | A 41 | LV DS B _ DA T A# _ 1 | AP | ||||

A V 4 2 |

|

|

|

|

|

| 1 2 | G M_ LV DS _ U1 N | GM_ LV D S _U1 N | H 38 | |||||||

|

|

|

|

|

|

|

|

| LV DS B _ DA T A# _ 0 |

| |||||||

A R3 6 | Z 05 6 1 | R20 7 | * 10 mi l _s ho rt |

| 1. 5 V _P W RG D | 15 ,3 1 | 1 2 | G M_ LV DS _ U2 N | GM_ LV D S _U2 N | G 37 | LV DS B _ DA T A# _ 2 | GR | |||||

B F 1 7 | Z 05 6 2 | R15 5 | 49 9_ | 1 %_ 04 |

|

|

|

|

|

|

|

| J 37 | LV DS B _ DA T A# _ 3 | |||

B C3 6 |

|

| DDR3 _ DRA MRS T # | 1 0 ,11 |

| 1 2 | G M_ LV DS _ U0 P | GM_ LV D S _U0 P | B 42 | ||||||||

B 3 8 |

|

|

|

|

|

|

|

| LV DS B _ DA T A_ 0 |

| |||||||

|

| CL K_ DRE F | 1 | 8 |

|

|

| 1 2 | G M_ LV DS _ U1 P | GM_ LV D S _U1 P | G 38 |

| |||||

A 3 8 |

|

|

|

|

| GM_ LV D S _U2 P | F 37 | LV DS B _ DA T A_ 1 |

| ||||||||

|

| CL K_ DRE F # | 18 |

|

|

| 1 2 | G M_ LV DS _ U2 P | LV DS B _ DA T A_ 2 | SS | |||||||

E 4 1 |

|

| CL K_ DRE F _ S S | 18 |

|

|

|

|

|

|

|

| K 37 | LV DS B _ DA T A_ 3 | |||

F 4 1 |

|

|

|

|

|

|

|

|

|

|

| ||||||

|

| C L K_ D R E F _ S S # 1 8 |

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

| ||||||

F 4 3 |

|

| CL K_ P CIE _ 3GP L L | 1 8 |

|

|

| D VT : F or P M | R 10 1 | 0 _ 04 | Z 05 8 1 | F 25 |

| RE | |||

E 4 3 |

|

|

|

|

| TV A _ DA C | |||||||||||

|

|

| CL K_ P CIE _ 3GP L L # | 1 8 |

|

|

|

| R 10 5 | 0 _ 04 | Z 05 8 2 | H 25 | |||||

A E 3 7 |

|

|

|

|

|

|

|

|

|

|

| R 11 1 | 0 _ 04 | Z 05 8 3 | K 25 | TV B _ DA C | EXP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| TV C _ DA C | TV |

A E 4 1 |

|

| DMI _ TX N0 | 14 |

|

|

|

|

|

|

|

|

|

| H 24 | TV _ RT N | |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

A E 4 7 |

|

| DMI _ TX N1 | 14 |

|

|

|

|

|

|

|

|

|

|

|

| - |

|

| DMI _ TX N2 | 14 |

|

|

|

|

| DV T: F o r P M |

|

|

|

|

| |||

A H3 9 |

|

| DMI _ TX N3 | 14 |

|

|

|

|

|

|

|

| C 31 |

| I | ||

A E 4 0 |

|

|

|

|

|

|

|

|

| R 11 9 | 0 _ 04 |

|

|

| TV _ DCON S EL _ 0 | ||

|

| DMI _ TX P 1 | 1 4 |

|

|

|

|

|

|

|

| E 32 | PC | ||||

A E 4 8 |

|

|

|

|

|

|

| R10 3 | 0 _ 04 |

|

|

|

| TV _ DCON S EL _ 1 | |||

A E 3 8 |

|

| DMI _ TX P 0 | 1 4 |

|

|

|

|

| R11 3 | 0 _ 04 |

|

|

|

|

| |

A H4 0 |

|

| DMI _ TX P 2 | 1 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| D MI _ TX P 3 | 1 4 |

|

|

|

|

|

|

|

|

|

|

|

|

| |

A E 3 5 |

|

|

| DMI _ RX N0 | 1 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| E 28 |

|

|

|

|

|

| |||||

A E 4 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CRT _B L UE |

|

|

|

| |||||||||

A E 4 6 |

|

|

| DMI _ RX N1 | 1 4 |

|

|

| 2 8 | GM_ D A C _ B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||

A H4 2 |

|

|

| DMI _ RX N2 | 1 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G 28 | CRT _G RE E N |

|

|

|

| ||||||

|

|

| DMI _ RX N3 | 1 4 |

|

|

| 2 8 | GM_ DA C _ G |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||

A D3 5 |

|

|

| DMI _ RX P0 | 1 4 |

|

|

| 2 8 | GM_ DA C _ R |

|

|

|

|

|

|

|

|

|

| J 28 | CRT _R ED |

|

| VG | ||||||||||||||||||

A E 4 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||

A H4 3 |

|

|

| DMI _ RX P2 | 1 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CRT _IRT N |

|

| ||||||||

A F 4 6 |

|

|

| DMI _ RX P1 | 1 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G 29 |

|

|

|

|

|

| |||||

|

|

|

|

| DMI _ RX P3 | 1 4 |

|

|

| 2 8 GM_ DDC _ CL K |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| H 32 | CRT _D DC _ CLK |

| A | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| J 32 |

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2 8 GM_ DDC _ DA T A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CRT _D DC _ DA TA |

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| R 80 | * 30 . 1_ 1 %_ 04 |

|

| CH | J 29 |

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| 2 8 | G M_ DA C _ HS Y NC |

|

|

|

|

| R 94 |

|

|

| 0 _ | 04 |

|

|

|

| Z 05 8 5 |

| E 29 | CRT _H SY NC |

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CV |

| L 29 | CRT _T V O_ IRE F |

|

|

| ||

B 3 3 |

|

|

|

|

|

|

|

|

|

|

| 2 8 G M_ DA C _ VS Y NC |

|

|

|

|

| R 75 | * 30 . 1_ 1 %_ 04 |

|

|

|

|

| CRT _V S Y N C |

|

|

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

B 3 2 |

|

|

|

|

| DF GT _ V DI _0 30 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

G3 3 |

|

|

|

|

| DF GT _ V DI | _1 | 30 |

|

|

|

|

|

|

|

|

| R 81 | 0 _ 04 | CH |

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

| DF GT _ V DI | _2 | 30 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

F 3 3 |

|

|

|

|

| D F GT _ V DI | _3 | 30 |

|

|

|

|

|

|

|

|

| R 74 |

|

|

|

| 0 _ | 04 | CV |

|

|

|

|

| CA NT IGA |

|

|

|

| ||||||||

E 3 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

| DF GT _ V DI _4 30 |

|

|

|

|

|

|

|

| R 12 7 | 0 _ 04 | L _C TRL _ CLK |

| 1 . 5V |

|

| 1 . 5V | ||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| R 11 2 |

|

|

|

| 0 _ | 04 | L _C TRL _ DA TA | K |

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| R 11 4 |

|

|

| 0 _ | 04 | GM _E DID _CL |

|

|

|

|

|

|

| ||||||||

C3 4 |

|

|

|

|

| DF GT _ V R _E N | 3 0 |

|

|

|

|

|

|

|

|

| R 85 |

|

|

| 0 _ | 04 | GM _E DID _DA | T A |

|

| R 15 7 |

| R 16 1 |

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1. 0 5V M |

|

|

|

|

| For PM |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 80 . 6_ 1 %_ 04 |

| |||||||

A H3 7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| M_V R EF _ MC H |

| 1 0 K _1 %_ 04 | S M _RC OMP |

| |||||||

|

|

| C L_ CL K0 | 1 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

A H3 6 |

|

|

| C L_ D A TA 0 | 15 |

|

|

|

| R1 47 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| S M_R COMP # |

| |||||||

A N3 6 |

|

|

|

| MP W ROK | 1 5 |

|

|

|

| 1 K _ 1% _0 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

A J 35 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C 25 3 |

| R 15 6 |

|

| |||||||||||

A H3 4 |

|

|

|

| C L _R ST # 0 | 1 5 |

| CL _V RE F |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 06 |

|

|

| R 16 0 | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

| C2 1 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3V_ |

| 1 0 K _1 %_ 04 | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| R 14 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 6. |

|

|

| 80 . 6_ 1 %_ 04 |

| ||

N2 8 | DDP C _CT _ CLK |

|

|

|

| 0 . 1u _1 0 V _0 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| u |

|

|

|

|

|

| ||||||||||

M2 8 | D D P C _C T _ D A TA |

|

|

|

|

|

|

| 5 1 1_ 1% _ 04 |

|

|

|

|

|

| 3. 3 V S |

|

|

|

|

|

| 2. 2 |

|

|

|

|

|

| ||||||||||||||

G3 6 | S DV O_ CT _CL K |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3. 3 V S |

|

|

|

|

|

|

| |||||||||||||||

E 3 6 | S DV O_ CT _DA T A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

K 3 6 | MCH _CL K RE Q# |

|

|

| MCH _ CL K RE Q# 18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

H3 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

| MCH _ ICH _S Y NC # | 1 5 |

|

|

|

|

|

|

|

|

|

|

|

| R 7 2 | R 7 8 |

|

| R7 7 |

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

| 1 . 0 5V S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||

B 1 2 | MCH _ TS A T N# | R3 68 | 5 6_ 04 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| *1 K _0 4 | *1 K _0 4 |

|

| 1 0K _ 1% _ 04 | MCH _ T HE RM | 2 2 |

|

|

| |||||||

B 2 8 | Z0 5 67 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 |

|

|

|

|

|

|

|

|

| |||||

B 3 0 | Z0 5 68 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C |

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

B 2 9 | Z0 5 69 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RT 1 |

|

|

|

|

|

|

| ||||

C2 9 | Z0 5 70 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| B |

|

|

|

|

| N TC _ 1 00 K _0 6 |

|

|

|

| |||||||||

A 2 8 | Z0 5 71 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C |

|

|

|

| Q2 1 |

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MCH _T S A TN # B |

|

|

|

| *2 N3 90 4 | 2 |

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| E |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Q5 1 |

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

| S DV O_ CT_ CL K |

| R 1 0 9 |

| *1 0 mi l s ho rt |

|

|

|

|

|

|

|

|

|

|

|

|

| *2 N 3 90 4 |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

| *1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

| S D V O_ C T_ D A T A R1 0 8 | 0 mi l s ho rt |

|

|

|

|

|

|

|

|

| E |

|

|

|

|

|

|

|

|

|

|

|

| 2 ,3,4 ,9,1 3,1 6 ,1 8 ,33 | 1. 0 5V S |

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

| For PM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 7 ,9 ,1 0,1 1,2 7 ,3 1 ,33 | 1. 5 V |

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2 ,3,9 ,12 ,13 ,1 4,1 5,1 6 ,1 9 ,20 ,21 ,22 ,2 3,2 4,2 5 ,2 6 ,28 ,30 ,32 ,3 3,3 5,3 6 ,3 7 ,38 | 3. 3 V S |

| |||||||||||||||||||||||

|

|

|

|

| T 37 |

| P E G _CO MP | R | 12 8 |

|

|

|

|

|

| |||||

|

| P E G_ COMP I |

| T 36 |

|

|

|

|

|

|

|

|

|

|

|

| V CC _ P E G | |||

| P E G_C OMP O |

|

|

|

|

| 4 9 | . 9_ 1% _0 4 |

|

|

| |||||||||

|

| P E G_ RX #_ 0 |

| H4 | 4 |

|

| P E G_ RX N0 |

|

|

|

|

| |||||||

|

|

| J 46 |

|

|

| P E G_ RX N1 |

|

|

|

|

| ||||||||

|

| P E G_ RX #_ 1 |

| L 44 |

|

|

| P E G_ RX N2 |

|

|

|

|

| |||||||

|

| P E G_ RX #_ 2 |

| L 40 |

|

|

| P E G_ RX N3 |

|

|

|

|

| |||||||

|

| P E G_ RX #_ 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| N4 1 |

|

| P E G_ RX N4 |

|

|

|

|

| |||||||||

|

| P E G_ RX #_ 4 |

| P 4 8 |

|

| P E G_ RX N5 |

|

|

|

|

| ||||||||

|

| P E G_ RX #_ 5 |

| N4 4 |

|

|

| P E G_ RX N6 |

|

|

|

|

| |||||||

|

| P E G_ RX #_ 6 |

| T 43 |

|

| P E G_ R X N 7 |

|

|

|

|

| ||||||||

|

| P E G_ RX #_ 7 |

| U4 3 |

|

| P E G_ RX N8 |

|

|

|

|

| ||||||||

|

| P E G_ RX #_ 8 |

| Y 4 3 |

|

| P E G_ RX N9 |

|

|

|

|

| ||||||||

|

| P E G_ RX #_ 9 |

| Y 4 8 |

|

|

| P E G_ RX N1 | 0 |

|

|

|

| |||||||

| P E G _RX # _1 0 |

| Y 3 6 |

|

|

| P E G_ RX N1 1 |

|

|

| ||||||||||

| P E G _RX # _1 1 |

| A A 4 3 |

|

| P E G_ RX N1 2 |

|

|

| |||||||||||

| P E G _RX # _1 2 |

| A D3 7 |

|

| P E G_ RX N1 3 |

|

|

| |||||||||||

| P E G _RX # _1 3 |

| A C4 7 |

|

| P E G_ RX N1 4 |

|

|

| |||||||||||

| P E G _RX # _1 4 |

| A D3 9 |

|

| P E G_ RX N1 5 |

|

|

| |||||||||||

| P E G _RX # _1 5 |

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

| P EG _R X_ 0 |

| H4 3 |

|

| P E G_ RX P | 0 |

|

|

|

|

| ||||||

|

|

|

| J 44 |

|

|

| P E G_ RX P 1 |

|

|

|

|

| |||||||

|

|

| P EG _R X_ 1 |

| L 43 |

|

|

| P E G_ RX P 2 |

|

|

|

|

| ||||||

|

|

| P EG _R X_ 2 |

| L 41 |

|

|

| P E G_ RX P 3 |

|

|

|

|

| ||||||

|

|

| P EG _R X_ 3 |

| N4 0 |

|

|

| P E G_ RX P | 4 |

|

|

|

|

| |||||

|

|

| P EG _R X_ 4 |

| P 4 7 |

|

| P E G_ R X P 5 |

|

|

|

|

| |||||||

|

|

| P EG _R X_ 5 |

| N4 3 |

|

| P E G_ RX P 6 |

|

|

|

|

| |||||||

|

|

| P EG _R X_ 6 |

| T 42 |

|

| P E G_ RX P 7 |

|

|

|

|

| |||||||

|

|

| P EG _R X_ 7 |

| U4 2 |

|

|

| P E G_ RX P 8 |

|

|

|

|

| ||||||

|

|

| P EG _R X_ 8 |

| Y 4 2 |

|

| P E G_ RX P 9 |

|

|

|

|

| |||||||

|

|

| P EG _R X_ 9 |

| W 4 7 |

|

|

|

|

|

|

|

|

|

| |||||

|

| P E G_ RX _1 0 |

| Y 3 7 |

|

| P E G_ RX P 11 |

|

|

| ||||||||||

|

| P E G_ RX _1 1 |

| A A 4 2 |

|

| P E G_ RX P 12 |

|

|

| ||||||||||

|

| P E G_ RX _1 2 |

| A D3 6 |

| P E G_ RX P 13 |

|

|

| |||||||||||

|

| P E G_ RX _1 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| A C4 8 |

| P E G_ RX P 14 |

|

|

| ||||||||||||

|

| P E G_ RX _1 4 |

|

|

|

|

|

|

|

|

|

| ||||||||

|

| P E G_ RX _1 5 |

| A D4 | 0 |

|

| P E G_ RX P | 15 |

|

|

|

| |||||||

|

|

| J 41 G TN 0 C 1 55 | 0. 1 u_ 1 0V _ 04 | P E G_T X N0 | |||||||||||||||

|

| P E G_T X #_ 0 |

| M4 6 |

| G TN 1 C1 | 74 | 0. 1 | u_ 1 0V _ 04 | P E G_T X N1 |

| |||||||||

|

| P E G_T X #_ 1 |

| M4 7 |

| G TN 2 C1 | 53 | 0. 1 | u_ 1 0V _ 04 | P E G_T X N2 |

| |||||||||

|

| P E G_T X #_ 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| M4 0 |

| G TN 3 | C1 72 | 0. 1 u_ | 1 | 0V _ 04 | P E G_T X N3 | ||||||||||

|

| P E G_T X #_ 3 |

| M4 2 |

| G TN 4 C1 | 51 | 0. 1 | u_ 1 0V _ 04 | P E G_T X N 4 |

| |||||||||

|

| P E G_T X #_ 4 |

| R4 8 |

| G TN 5 C1 | 70 | 0. 1 | u_ 1 0V _ 04 | P E G_T X N5 |

| |||||||||

|

| P E G_T X #_ 5 |

| N3 8 |

| G TN 6 C1 | 49 | 0. 1 | u_ 1 0V _ 04 | P E G_T X N6 |

| |||||||||

|

| P E G_T X #_ 6 |

| T 40 | G TN 7 C1 | 68 | 0. 1 | u_ 1 0V _ 04 | P E G_T X N7 |

| ||||||||||

|

| P E G_T X #_ 7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

| P E G_T X #_ 8 |

| U3 7 |

| G TN 8 C1 47 | 0. 1 u_ 1 0V _ 04 | P E G_T X N 8 | ||||||||||||

|

| P E G_T X #_ 9 |

| U4 0 |

| G TN 9 | C1 | 67 | 0. 1 | u_ 1 | 0V _ 04 | P E G_T X N9 |

| |||||||

|

|

| Y 4 0 |

| G TN 10 C1 | 46 | 0. 1 | u_ 1 | 0V _ 04 | P E G_T X N10 |

| |||||||||

|

| P E G_ TX # _1 0 |

| A A 4 | 6 | G TN 11 C1 | 64 | 0. 1 | u_ 1 | 0V _ 04 | P E G_T X N11 |

| ||||||||

|

| P E G_ TX # _1 1 |

| A A 3 | 7 | G TN 12 C1 | 62 | 0. 1 | u_ 1 | 0V _ 04 | P E G_T X N12 |

| ||||||||

|

| P E G_ TX # _1 2 |

| A A 4 | 0 | G TN 13 C1 | 42 | 0. 1 | u_ 1 | 0V _ 04 | P E G_T X N13 |

| ||||||||

|

| P E G_ TX # _1 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| A D4 | 3G TN 14 C1 61 | 0. 1 u_ 1 | 0V _ 04 | P E G_T X N14 | |||||||||||||||

|

| P E G_ TX # _1 4 |

| A C4 | 6 | G TN 15 C1 | 44 | 0. 1 | u_ 1 | 0V _ 04 | P E G_T X N15 |

| ||||||||

|

| P E G_ TX # _1 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| P E G_ T X_ 0 |

| J 42 G TP 0 C 1 56 | 0. 1 u_ 1 0V _ 04 | P E G_T X P0 | |||||||||||||

|

|

|

| L 46 | G TP 1 C1 | 75 | 0. 1 | u_ 1 0V _ 04 | P E G_T X P1 |

| ||||||||||

|

|

| P E G_ T X_ 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| M4 8 |

| G TP 2 C1 54 | 0. 1 u_ 1 0V _ 04 | P E G_T X P2 | |||||||||||||||

|

|

| P E G_ T X_ 2 |

|

| |||||||||||||||

|

|

| P E G_ T X_ 3 |

| M3 9 |

| G TP 3 | C1 | 73 | 0. 1 | u_ 1 | 0V _ 04 | P E G_T X P3 |

| ||||||

|

|

|

| M4 3 |

| G TP 4 C 1 | 52 | 0. 1 | u_ 1 0V _ 04 | P E G_T X P4 |

| |||||||||

|

|

| P E G_ T X_ 4 |

| R4 7 |

| G TP 5 C1 | 71 | 0. 1 | u_ 1 0V _ 04 | P E G_T X P5 |

| ||||||||

|

|

| P E G_ T X_ 5 |

| N3 7 |

| G TP 6 C1 | 50 | 0. 1 | u_ 1 0V _ 04 | P E G_T X P6 |

| ||||||||

|

|

| P E G_ T X_ 6 |

| T 39 |

| G TP 7 C1 | 69 | 0. 1 | u_ 1 0V _ 04 | P E G_T X P7 |

| ||||||||

|

|

| P E G_ T X_ 7 |

| U3 6 |

| G TP 8 C 1 48 | 0. 1 u_ 1 0V _ 04 | P E G_T X P8 | |||||||||||

|

|

| P E G_ T X_ 8 |

| U3 9 |

| G TP 9 C1 | 66 | 0. 1 | u_ 1 0V _ 04 | P E G_T X P9 |

| ||||||||

|

|

| P E G_ T X_ 9 |

| Y 3 9 |

| G TP 1 0 C1 | 45 | 0. 1 | u_ 1 0V _ 04 | P E G_T X P1 0 |

| ||||||||

|

| P E G_T X _1 0 |

| Y 4 6 |

| G TP 1 1 C 1 | 65 | 0. 1 | u_ 1 0V _ 04 | P E G_T X P1 1 |

| |||||||||

|

| P E G_T X _1 1 |

| A A 3 6 | G TP 1 2 C1 | 63 | 0. 1 | u_ 1 0V _ 04 | P E G_T X P1 2 |

| ||||||||||

|

| P E G_T X _1 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

| P E G_T X _1 3 |

| A A 3 9G TP 1 3 C1 41 | 0. 1 u_ 1 0V _ 04 | P E G_T X P1 3 | ||||||||||||||

|

| P E G_T X _1 4 |

| A D4 2 | G TP 1 4 C1 | 60 | 0. 1 | u_ 1 0V _ 04 | P E G_T X P1 4 |

| ||||||||||

|

|

| A D4 6 | G TP 1 5 C1 | 43 | 0. 1 | u_ 1 0V _ 04 | P E G_T X P1 5 |

| |||||||||||

|

| P E G_T X _1 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| 1 5. V | R1 6 4 |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

| S M_ RCO MP _V OH |

|

|

| 1K _ 1% _0 4 |

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

| C2 51 |

|

| C 25 5 |

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| 0 . 01 u_ 5 0V _ 04 | 2 . 2u _6 . 3V _ 0 6 | R1 6 2 |

|

|

|

|

| |||||||||||

|

|

| S M _RC OMP _ VO L |

|

|

| 3. 0 1K _ | 1% _ 04 |

|

|

| |||||||||

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

| C2 52 |

|

| C 25 4 |

|

|

| R 1 6 3 |

|

|

|

|

| |||||

|

| 0 . 01 u_ 5 0V _ 04 | 2. 2 u_ 6 . 3V _ 06 | 1K _ 1% _0 4 |

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3 . 3V S |

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

P M _E X TT S 0# |

| R 12 1 |

| 1 0K _ 0 4 |

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

P M _E X TT S 1# |

| R 12 5 |

| 1 0K _ 0 4 |

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B - 6 Cantiga 2/6, PEG